Vivado在线调试概述

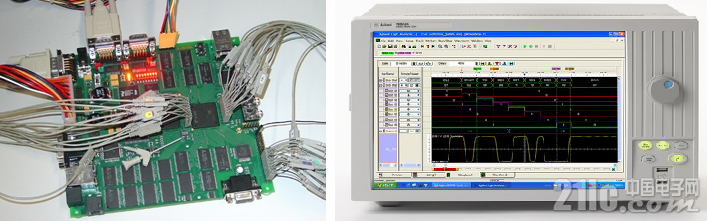

Vivado在线调试概述FPGA的板级调试方法有很多,借助于常规的示波器和逻辑分析仪的调试方法是最典型的手段。如图13.1所示,基于传统的台式示波器或逻辑分析仪进行板级调试有着诸多的不便,相对于设计电路深藏在芯片内部的FPGA设计来说有着很大的局限性,简单的列举如下。

● 台式机器价格昂贵,设备成本高。● 只能访问到FPGA的I/O引脚信号,对内部信号只能通过引出到I/O引脚的方式进行观察,并且此方式只有个别信号可行,大量内部信号就无能为力了。● PCB的layout设计必须预留足够的空间用于外部探针对被测试信号的连接,浪费板级空间且降低了电路可靠性,同时也会潜在的增加成本。● 测试信号较多,调试过程极其繁琐并容易犯错。● 灵活性差,只能观察设计之初就预留了探针接口的一些信号。

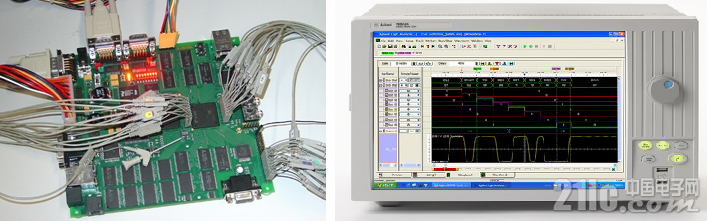

图 基于传统逻辑分析仪的板级调试 当然了,这些局限性在大多数产品的板级调试中都存在,尤其是在芯片集成度越来越高的当下。而FPGA器件由于其灵活的可编程特性,也使得它具有了更加独特的调试手段。在FPGA器件支持并且剩余逻辑资源足够的情况下,设计者往往习惯于使用开发软件提供的在线逻辑分析仪进行调试,如Vivado的ILA和QuartusII的SignalTapII,它们的功能都很强大,并且非常的简单实用。它们相较于传统的台式仪器,不仅大大降低了调试门槛和成本,而且由于其内嵌于FPGA器件的特性,使得其可调试性和灵活性上也更胜一筹,例如它可以访问到FPGA内部的一些中间过程信号。除此以外,还有一些其它的手段在不同的应用背景下都有助于加速板级调试。除此之外,还有类似虚拟IO、在线存储器编辑、Virtual JTAG之类的调试手段,都是非常简单实用的在线调试方法。下面我们看看Vivado中支持的一些重要调试方式。

ILA(Integrated LogicAnalyzer),即内嵌逻辑分析仪。可以在FPGA器件上对已实现的设计进行板级在线调试。ILA可用于板级调试过程中监测FPGA内部信号的实时状态,ILA也可用于硬件事件触发后以系统时钟频率采集信号。ILA和一般台式的逻辑分析仪功能基本相似,只不过台式逻辑分析仪是看得见摸得着的实物设备,且它必须对所有触发或观察信号进行物理连接,信号也必须在电路板上有实际的触点可供探测。但是ILA不同,你可以说它是一个软件工具而已,因为它只需要被测试设备本身(即FPGA器件),通过一条JTAG下载器与PC连接,在PC的Vivado上可以查看最终采集的波形。并且ILA不需要被测试信号有实际的物理探测点,只要这个信号是在FPGA内部,就可以被实时的观测到。ILA功能模块可以通过配置IP核方式例化到RTL代码中,也可以在Vivado的工具选项上直接加载设置。

VIO(Virtual Input/Output),即虚拟IO调试接口。VIO可以用于实时的监控或驱动FPGA内部信号状态。如果对目标硬件缺乏合适的访问通信方式时,可以使用VIO功能实现FPGA内部信号实时的监控或驱动。VIO调试应用的主要场景可能是速率要求不高,但又希望可以在线交互的一些信号接口,比如一些开关信号的控制或状态信号的实时查看。VIO功能模块只能通过配置IP核方式例化到RTL代码中,设计代码中需要施加激励或者观察状态的信号必须通过VIO的IP核模块例化连接好。

IBERT(Integrated Bit ErrorRatio Tester),即内嵌误码率测试机。IBERT是针对高速串行接口的在线调试和验证。通过IBERT的检测,可以确认FPGA内部的高速串行口传输数据的可靠性和稳定性。

JTAG-to-AXI Master,即JTAG-to-AXI主机调试接口。对于不含处理器,但又有AXI从机接口的应用,该调试方式可以对设计中的AXI从机接口进行板级的在线调试验证。 以上所提的这些在线调试方式大都是通过FPGA器件引出的JTAG接口,同时使用了一些FPGA片内固有的逻辑、存储器或布线资源就能够实现的。这些调试功能通常也只需要随着用户设计所生产的配置文件一同下载到目标FPGA器件中运行。相比于复杂的传统台式仪器,基于FPGA的在线调试仅需一条JTAG线缆连接FPGA和PC机,非常简单清爽,调试起来更是得心应手。 至于我们所提到的这些在线调试手段,可以根据不同的应用和设计进行选择。因为不同的设计往往会有不同的约束和需求,例如可以根据闲置不使用引脚的数量、逻辑和存储器资源剩余量大小等进行不同的在线调试方式选择。 对于FPGA内部的在线调试,通常可以分为以下3个阶段。● 探测阶段:识别出需要进行探测的信号,确认使用何种在线调试手段进行探测。● 实现阶段:将在线调试的IP核集成到设计工程中,完成编译并生成板级调试的下载配置文件。● 分析阶段:使用集成的调试功能模块对设计功能进行验证和调试。

一周热门 更多>