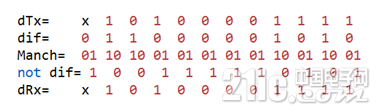

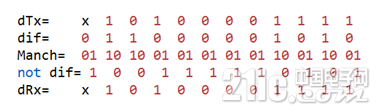

对于通信或计算机类专业来说,Manchester编码的概念应该人尽皆知。就是要把0编码成01,把1编码成10。“曼码”编码规则非常简单,解码也很容易。但是曼码解码时需要实现两个比特组合的对齐,换句话说,如果发端持续发送1而不发送0,那么接收端就无法保证正确解码。这种现象我们在此称之为曼码的相位模糊。如何解决曼码的相位模糊问题呢?方法是在曼彻斯特编码之前先进行差分编码,即用当前比特与前一比特相同表示0,用当前比特与前一比特相反表示1。例下图所示

dTx表示原始数据流,dif是差分编码数据,Manch是差分码流。那么在解码时只需要对Manch码每两个比特读取一个比特,读取的结果可能是dif,也可能是not dif。无论是哪一种情况,只需要对读取的结果取一次差分(当前比特与前一比特的异或),恢复的dRx与dTx完全相同。

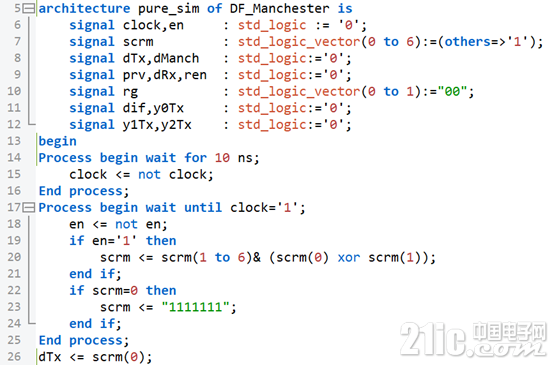

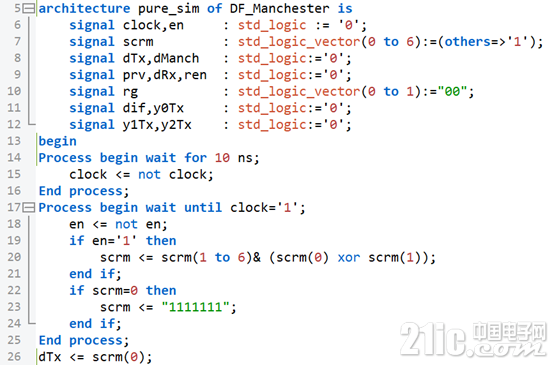

VHDL代码如下图所示。

前26行用于产生仿真用随机数据流dTx,行20是伪随机发生器

行18的en为发送使能,用作二分频。二分频的原因是曼码把线路速率提高了一倍,如果每个时钟发送一个曼码比特,那么需要每两个时钟产生一比特数据源。行26用dTx指明发送数据流。

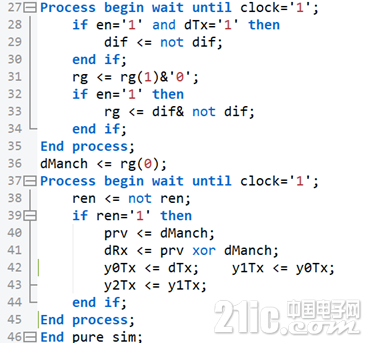

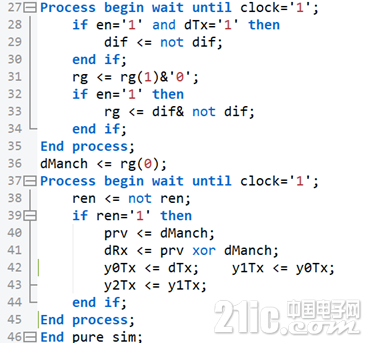

接下来是行27到46,如下图所示。

行29是差分编码,获得差分码dif。

行33是曼彻斯特编码

行31是按照时钟节拍把曼码的两个比特顺序移出。

36行之前,是对发送的仿真,dManch是发送的比特流。在接收端dManch是接收的比特流,36行之后是对接收解码的仿真。

行38使用ren而不使用en是为了表明接收的二分频与发送的二分频没有相位关系。

行40中prv表示前一个比特。

行41是解码,获得dRx。

行42和43是为了延时dTx,使得在仿真结果中y2Tx与dRx完全相同。

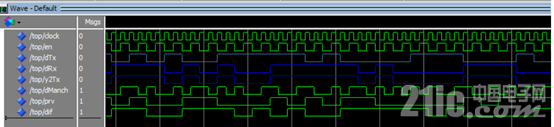

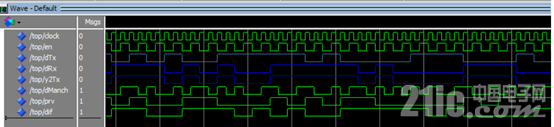

仿真结果如下图所示。

dTx表示原始数据流,dif是差分编码数据,Manch是差分码流。那么在解码时只需要对Manch码每两个比特读取一个比特,读取的结果可能是dif,也可能是not dif。无论是哪一种情况,只需要对读取的结果取一次差分(当前比特与前一比特的异或),恢复的dRx与dTx完全相同。

VHDL代码如下图所示。

前26行用于产生仿真用随机数据流dTx,行20是伪随机发生器

行18的en为发送使能,用作二分频。二分频的原因是曼码把线路速率提高了一倍,如果每个时钟发送一个曼码比特,那么需要每两个时钟产生一比特数据源。行26用dTx指明发送数据流。

接下来是行27到46,如下图所示。

行29是差分编码,获得差分码dif。

行33是曼彻斯特编码

行31是按照时钟节拍把曼码的两个比特顺序移出。

36行之前,是对发送的仿真,dManch是发送的比特流。在接收端dManch是接收的比特流,36行之后是对接收解码的仿真。

行38使用ren而不使用en是为了表明接收的二分频与发送的二分频没有相位关系。

行40中prv表示前一个比特。

行41是解码,获得dRx。

行42和43是为了延时dTx,使得在仿真结果中y2Tx与dRx完全相同。

仿真结果如下图所示。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>