例说FPGA连载97:基于HDMI的AV采集显示之hdmi_controller.v模块代码解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

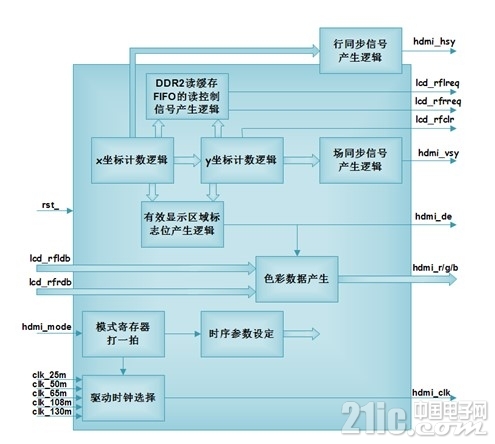

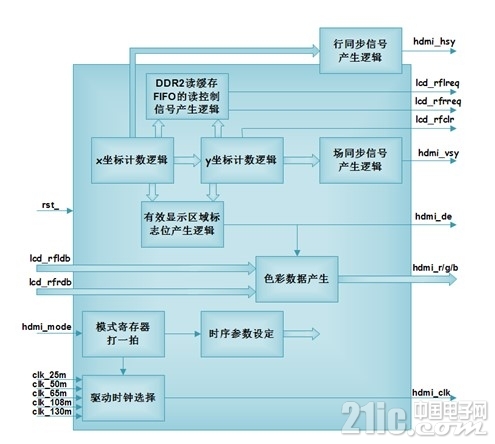

该模块产生多分辨率的HDMI显示驱动逻辑,将AV视频采集到的图像送到HDMI终端显示器。该模块的内部功能框图如图19.5所示。X、Y坐标计数器产生基本的HDMI时序,如hdmi_hsy、hdmi_vsy、hdmi_de等基本同步信号;同时,也产生DDR2读缓存FIFO的读端口控制信号,如FIFO读请求lcd_rflreq和lcd_rfrreq、FIFO清除信号lcd_rfclr。FIFO读出的数据总线lcd_rfldb和lcd_rfrdb最终将送到HDMI显示器上。

图19.5 HDMI驱动模块功能框图 关于“一拖四”的实现,思路是这样的:在ddr_avl_bridge.v模块中定义两个用于缓存DDR2读出数据的FIFO,这两个FIFO从DDR2送来的输入的数据是完全一致的,它们分别由不同的请求信号lcd_rflreq和lcd_rfrreq触发读取操作。即在同一行要显示两个相同的视频图像,那么每一行视频数据就要被读取两次,逻辑中产生读请求信号lcd_rflreq和lcd_rfrreq就是左半屏和右半屏分开实现,其逻辑代码如下。 //读取DDR2中640*480的AV图像请求信号(左侧视频)always @(posedge clk or negedge rst_n) if(!rst_n) lcd_rflreq <= 1'b0; else if((ycnt >=(VGA_VST+VGA_VBP)) && (ycnt < (VGA_VST+VGA_VBP+960)) &&(xcnt >= (VGA_HST+VGA_HBP-2)) && (xcnt <(VGA_HST+VGA_HBP-2+640))) lcd_rflreq <= 1'b1; else lcd_rflreq <= 1'b0; //读取DDR2中640*480的AV图像请求信号(右侧视频)always @(posedge clk or negedge rst_n) if(!rst_n) lcd_rfrreq <= 1'b0; else if((ycnt >=(VGA_VST+VGA_VBP)) && (ycnt < (VGA_VST+VGA_VBP+960)) &&(xcnt >= (VGA_HST+VGA_HBP-2+640)) && (xcnt <(VGA_HST+VGA_HBP-2+1280))) lcd_rfrreq <= 1'b1; else lcd_rfrreq <= 1'b0; 此外,我们将显示的上半屏幕和下半屏幕分别进行完整的图像读取,很容易就实现上下屏幕图像的“复制”。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

感謝你的恩德

小弟收下了

學習中

感謝

...給你一個讚

一周热门 更多>