#include "fsmc.h"

#include "delay.h"

#define Bank1_SRAM1_ADDR ((u32)(0x60000000))

void FSMC_Init(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure; //定义FSMC初始化的结构体变量

FSMC_NORSRAMTimingInitTypeDef readWriteTiming; //用来设置FSMC读时序和写时序的指针变量

GPIO_InitTypeDef GPIO_InitStructure; //初始化FSMC总线的IO口

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD|RCC_APB2Periph_GPIOE|RCC_APB2Periph_AFIO, ENABLE);

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE);

//----------------------------初始化GPIO_D GPIO_E---------------------------

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_14|GPIO_Pin_15|GPIO_Pin_0|GPIO_Pin_1|GPIO_Pin_8|GPIO_Pin_9|GPIO_Pin_10|GPIO_Pin_11|GPIO_Pin_12|GPIO_Pin_13|GPIO_Pin_4|GPIO_Pin_5|GPIO_Pin_7;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //IO口配置为复用推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7|GPIO_Pin_8|GPIO_Pin_9|GPIO_Pin_10|GPIO_Pin_11|GPIO_Pin_12|GPIO_Pin_13|GPIO_Pin_14|GPIO_Pin_15;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOE, &GPIO_InitStructure);

//---------------------------读写时序----------------------------------------

readWriteTiming.FSMC_AddressSetupTime = 14; //地址建立时间(ADDSET)

readWriteTiming.FSMC_AddressHoldTime = 0; //地址保持时间(ADDHLD)模式A未用到

readWriteTiming.FSMC_DataSetupTime = 15; //数据保持时间(DATAST)

readWriteTiming.FSMC_BusTurnAroundDuration = 0;

readWriteTiming.FSMC_CLKDivision = 0;

readWriteTiming.FSMC_DataLatency = 0;

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

//----------------------------FSMC初始化---------------------------------------

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1; //这是使用NE1

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE);

delay_ms(20);

}

//写函数

void FSMC_FPGA_WriteByte(u8 WriteAddr,u16 data)

{

*((volatile unsigned short int*)(Bank1_SRAM1_ADDR + (WriteAddr<<17))) = data;

}

//向指定地址发送数据

int main(void)

{

delay_init(); //延时函数初始化

uart_init(115200); //串口初始化为115200

FSMC_Init(); //初始化FSMC接口

while(1)

{

FSMC_FPGA_WriteByte(0,0x2000);

FSMC_FPGA_WriteByte(1,0x3000);

FSMC_FPGA_WriteByte(2,0x4000);

FSMC_FPGA_WriteByte(3,0x5000);

FSMC_FPGA_WriteByte(4,0x6000);

FSMC_FPGA_WriteByte(5,0x7000);

FSMC_FPGA_WriteByte(6,0x8000);

FSMC_FPGA_WriteByte(7,0x9000);

}

//------------------------------------下面为FPGA接收STM32发送数据的程序-------------

module fsmc(

clk,

ab, //address

db, //data

wrn, //wr

rdn, //rd

rst_n, //resetn

csn //cs

);

input[2:0] ab;

inout[15:0] db; //inout 定义db为双向端口

input wrn;

input rdn;

input rst_n;

input csn;

input clk;

reg [15:0] outa;

reg [15:0] outb;

reg [15:0] outc;

reg [15:0] outd;

reg [15:0] oute;

reg [15:0] outf;

reg [15:0] outg;

reg [15:0] outh;

wire rd;

wire wr;

reg [15:0] indata;

reg wr_tmp1;

reg wr_tmp2;

//assign wr = !(csn & wrn); //低电平使能 -> 高

assign rd = ~csn & ~rdn; //低电平使能 -> 高

//assign db = rd ? indata:16'hzzzz;//三态门

always @(posedge clk) //注意这里是为了与时钟同步

begin

wr_tmp1 <= wr;

wr_tmp1 <= wr_tmp1;

end

wire WR_FALLING = wr_tmp2 & ~wr_tmp1;//下降沿写

always @(*) //组合电路,只要变化就写

begin

if(!rst_n)begin

outa<=16'h0000;

outb<=16'h0000;

outc<=16'h0000;

outd<=16'h0000;

oute<=16'h0000;

outf<=16'h0000;

outg<=16'h0000;

outh<=16'h0000;

end

else begin

if(WR_FALLING)begin

case (ab)

3'b000:outa <= db;

3'b001:outb <= db;

3'b010:outc <= db;

3'b011:outd <= db;

3'b100:oute <= db;

3'b101:outf <= db;

3'b110:outg <= db;

3'b111:outh <= db;

default:;

endcase

end

end

end

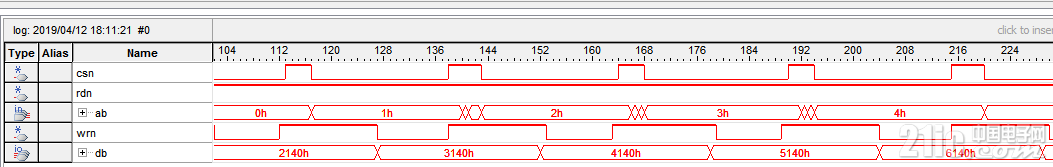

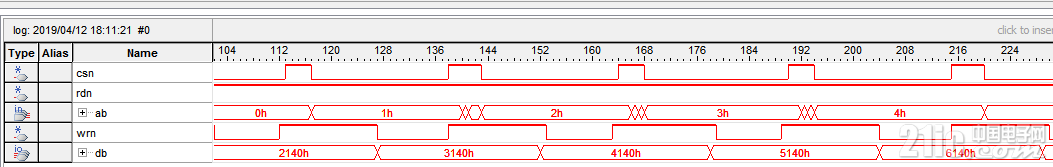

//下面为Signaltap的仿真图,问题来了,发送的数据2000,3000.........都变成2140,3140等,这是为啥,已经困扰一星期了,

花费了很多时间,还没解决,真心求帮助

#include "delay.h"

#define Bank1_SRAM1_ADDR ((u32)(0x60000000))

void FSMC_Init(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure; //定义FSMC初始化的结构体变量

FSMC_NORSRAMTimingInitTypeDef readWriteTiming; //用来设置FSMC读时序和写时序的指针变量

GPIO_InitTypeDef GPIO_InitStructure; //初始化FSMC总线的IO口

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD|RCC_APB2Periph_GPIOE|RCC_APB2Periph_AFIO, ENABLE);

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE);

//----------------------------初始化GPIO_D GPIO_E---------------------------

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_14|GPIO_Pin_15|GPIO_Pin_0|GPIO_Pin_1|GPIO_Pin_8|GPIO_Pin_9|GPIO_Pin_10|GPIO_Pin_11|GPIO_Pin_12|GPIO_Pin_13|GPIO_Pin_4|GPIO_Pin_5|GPIO_Pin_7;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //IO口配置为复用推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7|GPIO_Pin_8|GPIO_Pin_9|GPIO_Pin_10|GPIO_Pin_11|GPIO_Pin_12|GPIO_Pin_13|GPIO_Pin_14|GPIO_Pin_15;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOE, &GPIO_InitStructure);

//---------------------------读写时序----------------------------------------

readWriteTiming.FSMC_AddressSetupTime = 14; //地址建立时间(ADDSET)

readWriteTiming.FSMC_AddressHoldTime = 0; //地址保持时间(ADDHLD)模式A未用到

readWriteTiming.FSMC_DataSetupTime = 15; //数据保持时间(DATAST)

readWriteTiming.FSMC_BusTurnAroundDuration = 0;

readWriteTiming.FSMC_CLKDivision = 0;

readWriteTiming.FSMC_DataLatency = 0;

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

//----------------------------FSMC初始化---------------------------------------

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1; //这是使用NE1

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE);

delay_ms(20);

}

//写函数

void FSMC_FPGA_WriteByte(u8 WriteAddr,u16 data)

{

*((volatile unsigned short int*)(Bank1_SRAM1_ADDR + (WriteAddr<<17))) = data;

}

//向指定地址发送数据

int main(void)

{

delay_init(); //延时函数初始化

uart_init(115200); //串口初始化为115200

FSMC_Init(); //初始化FSMC接口

while(1)

{

FSMC_FPGA_WriteByte(0,0x2000);

FSMC_FPGA_WriteByte(1,0x3000);

FSMC_FPGA_WriteByte(2,0x4000);

FSMC_FPGA_WriteByte(3,0x5000);

FSMC_FPGA_WriteByte(4,0x6000);

FSMC_FPGA_WriteByte(5,0x7000);

FSMC_FPGA_WriteByte(6,0x8000);

FSMC_FPGA_WriteByte(7,0x9000);

}

//------------------------------------下面为FPGA接收STM32发送数据的程序-------------

module fsmc(

clk,

ab, //address

db, //data

wrn, //wr

rdn, //rd

rst_n, //resetn

csn //cs

);

input[2:0] ab;

inout[15:0] db; //inout 定义db为双向端口

input wrn;

input rdn;

input rst_n;

input csn;

input clk;

reg [15:0] outa;

reg [15:0] outb;

reg [15:0] outc;

reg [15:0] outd;

reg [15:0] oute;

reg [15:0] outf;

reg [15:0] outg;

reg [15:0] outh;

wire rd;

wire wr;

reg [15:0] indata;

reg wr_tmp1;

reg wr_tmp2;

//assign wr = !(csn & wrn); //低电平使能 -> 高

assign rd = ~csn & ~rdn; //低电平使能 -> 高

//assign db = rd ? indata:16'hzzzz;//三态门

always @(posedge clk) //注意这里是为了与时钟同步

begin

wr_tmp1 <= wr;

wr_tmp1 <= wr_tmp1;

end

wire WR_FALLING = wr_tmp2 & ~wr_tmp1;//下降沿写

always @(*) //组合电路,只要变化就写

begin

if(!rst_n)begin

outa<=16'h0000;

outb<=16'h0000;

outc<=16'h0000;

outd<=16'h0000;

oute<=16'h0000;

outf<=16'h0000;

outg<=16'h0000;

outh<=16'h0000;

end

else begin

if(WR_FALLING)begin

case (ab)

3'b000:outa <= db;

3'b001:outb <= db;

3'b010:outc <= db;

3'b011:outd <= db;

3'b100:oute <= db;

3'b101:outf <= db;

3'b110:outg <= db;

3'b111:outh <= db;

default:;

endcase

end

end

end

//下面为Signaltap的仿真图,问题来了,发送的数据2000,3000.........都变成2140,3140等,这是为啥,已经困扰一星期了,

花费了很多时间,还没解决,真心求帮助

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

你好,我还是不能够解决,一般都是32的写函数出问题了,您能在指导一下吗?诚心感谢!

代码很简单 重点看看db这个总线上的数据 是不是有两个bit位短接了或其他原因 不受控

FPGA的总线,相比STM32是很快的。

一周热门 更多>