本帖最后由 muelfox 于 2019-1-21 18:49 编辑

最近一有时间就在看Verilog, 然后就觉的没有开发板练习, 看到二姨家以前的一个开发板借用的活动, 就厚颜找@巧克力娃娃 借了一块锆石A4开发板, 这块板借了10几天了, 先发个简单的开箱个数码管工程, 工程没什么大用, 就是说明下这个开发板的使用

一. 开箱

拆开包裹, 见到的第一眼

有一张包装膜, 只好给破了 , 抽出来的那个盒子感觉有点厚重, 不是很好打开

, 抽出来的那个盒子感觉有点厚重, 不是很好打开

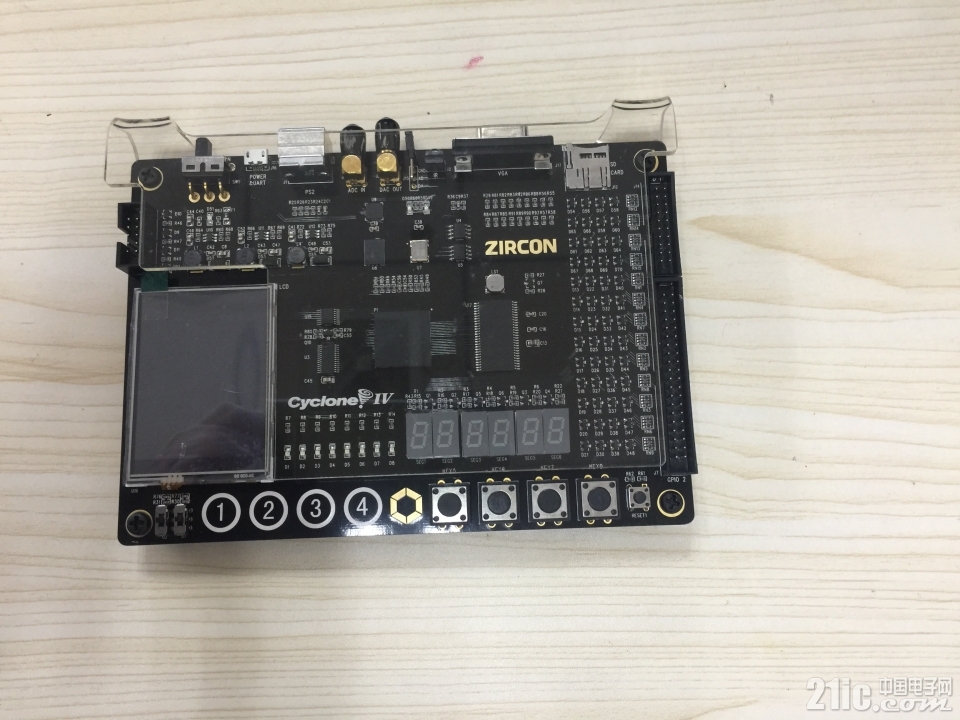

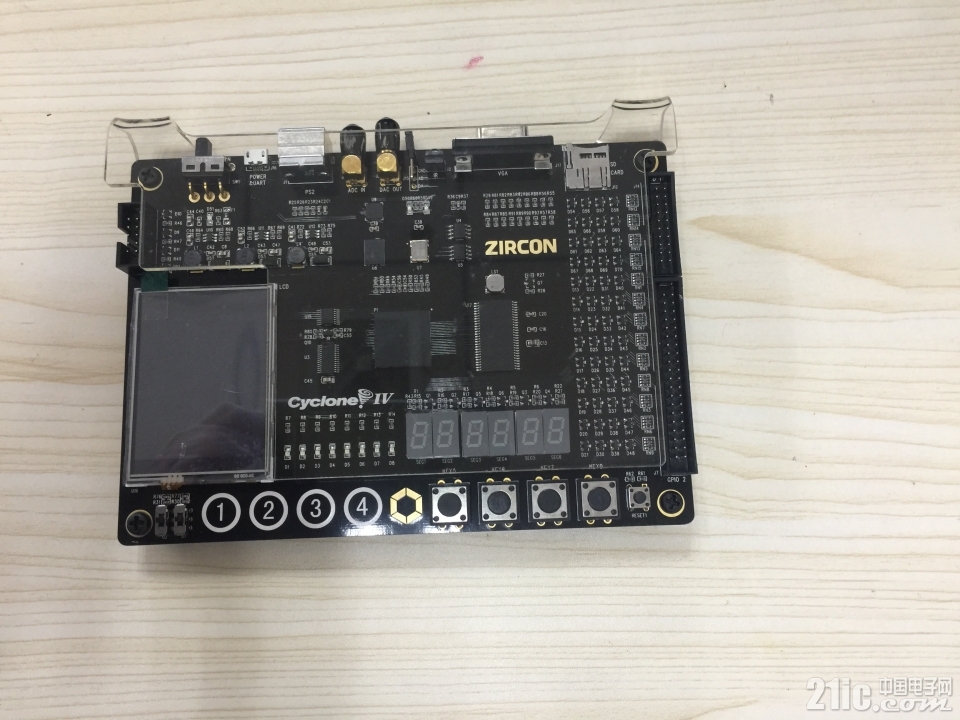

打开后能看到A4开发板, 有透明亚克力做的保护壳

开发板侧面接口

下面那层更难打开

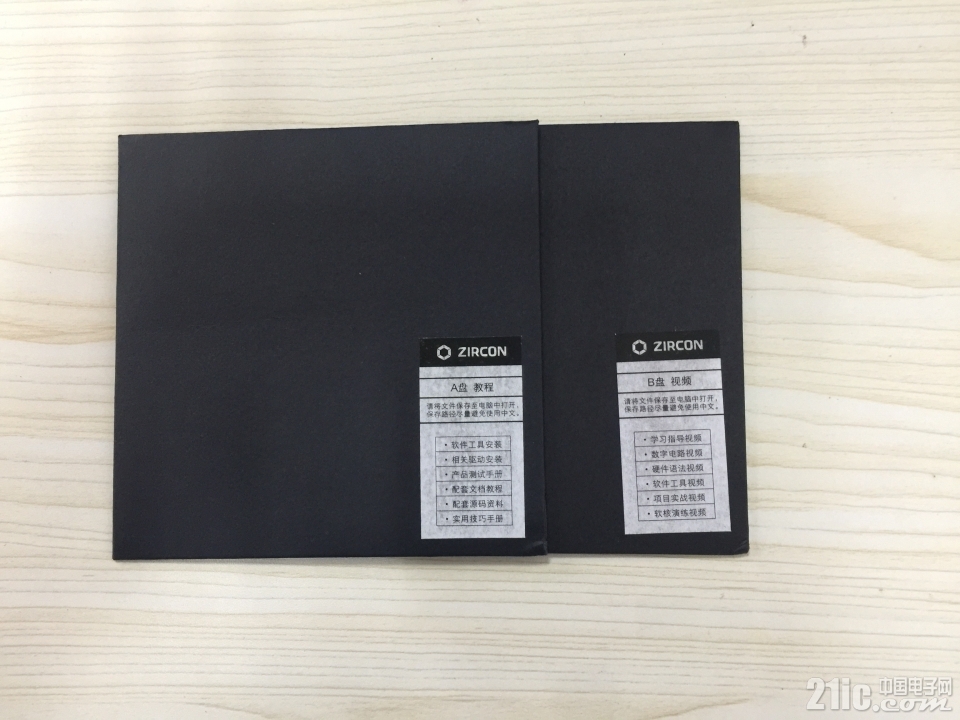

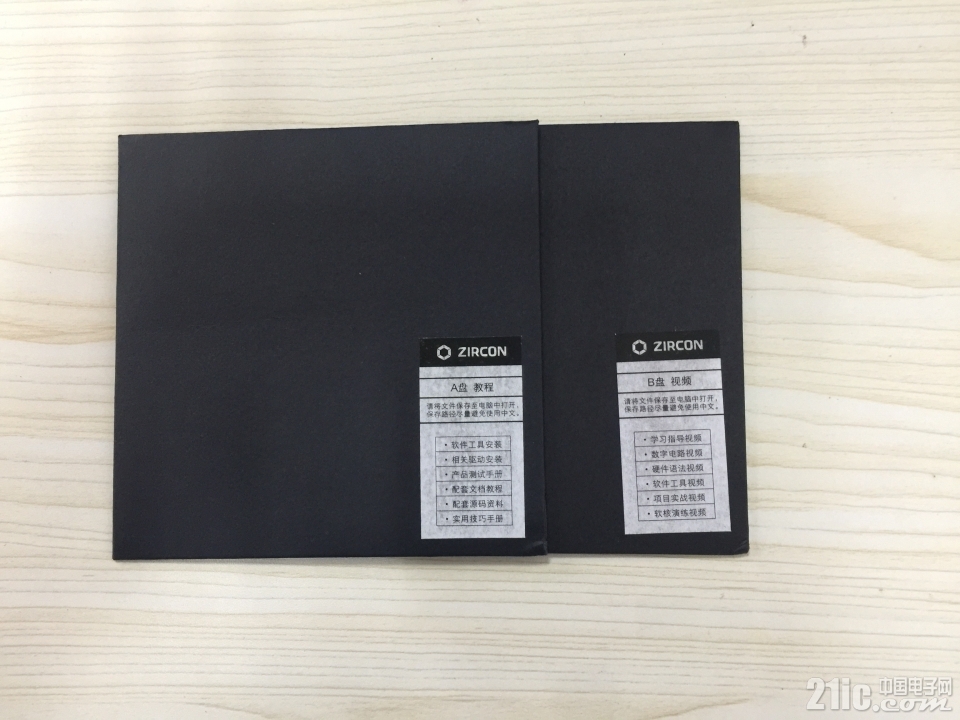

不过说真的, 那根USB线是真的真材实料, 下层的下面还有一个小盒子, 里面是光盘资料和一个说明书

然后就没有然后了, 这里不行不吐嘈下, 没看到USB-Blaster, 好吧, 什么都准备好了, 你给我说没有USB-Blaster , 只有找万能的X宝喽!

, 只有找万能的X宝喽!

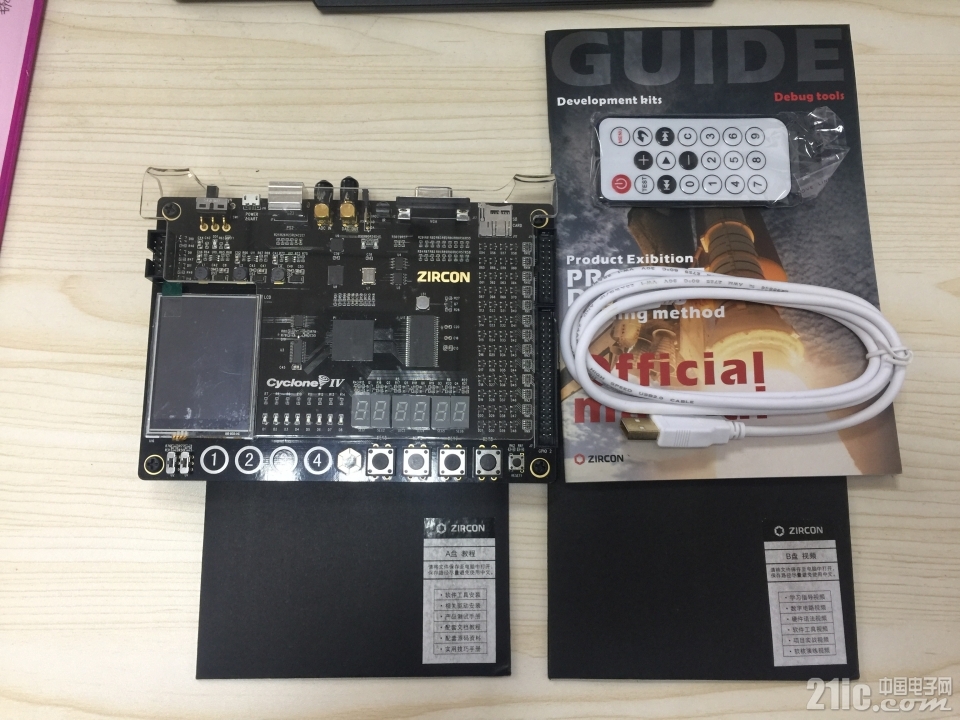

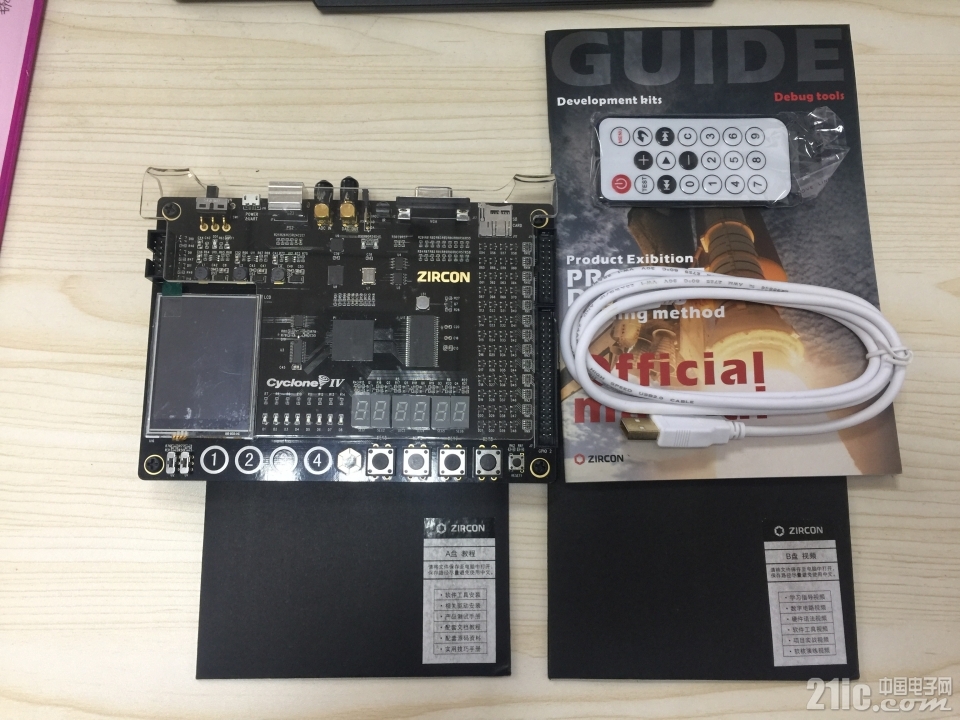

来张全家福

最近一有时间就在看Verilog, 然后就觉的没有开发板练习, 看到二姨家以前的一个开发板借用的活动, 就厚颜找@巧克力娃娃 借了一块锆石A4开发板, 这块板借了10几天了, 先发个简单的开箱个数码管工程, 工程没什么大用, 就是说明下这个开发板的使用

一. 开箱

拆开包裹, 见到的第一眼

有一张包装膜, 只好给破了

, 抽出来的那个盒子感觉有点厚重, 不是很好打开

, 抽出来的那个盒子感觉有点厚重, 不是很好打开

打开后能看到A4开发板, 有透明亚克力做的保护壳

开发板侧面接口

下面那层更难打开

不过说真的, 那根USB线是真的真材实料, 下层的下面还有一个小盒子, 里面是光盘资料和一个说明书

然后就没有然后了, 这里不行不吐嘈下, 没看到USB-Blaster, 好吧, 什么都准备好了, 你给我说没有USB-Blaster

, 只有找万能的X宝喽!

, 只有找万能的X宝喽!来张全家福

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

二. 软件安装

按照光盘中《软件安装指导手册》中, 一路Next,

进入漫长等待后能正常完成安装, 试了下把光盘内复制到硬盘再安装出错, 不知道什么原因, 可能是安装源有中文目录@_@

然后安装说明就没有了, 然后一个巨坑就出现了, 那就是如果你用30天试用证书的话, 综合是不会生成sof文件, 我当时的工程就烧录时没法进行, 然后只能各种百度, 没有结果, 最后仔细看综合信息, 才发现试用证书是不能生成sof的

破解的话要用13.1的破解器, 我就搞错用了13.0的, 结果就是综合时出现不支持EP4CE10F17C8 器件错误, 如果你也用错的话, 记得先恢复原版sys_cpt.dll才能再次破解成功

三. 新建工程

按照光盘中《软件工具篇》1.3章中, 新建工程:

选择器件时在" Name filiter" 中输入开发板的主芯片型号"EP4CE10F17C8"

EDA工具设置, 不过我的工程仿真出错, 暂时不知道哪里出错了

最好在系统中安装等宽的编程字体, 在Tools -> Options -> Text Editor -> Fonts 中修改显示字体

继续新建Verilog文件, 没有教程那么复杂

双击下左边的"Analy & Synthesis", 综合通过后会自动生成管脚分配文件

参照《管脚分配手册》

使用菜单 Assignments -> Pin Planner, 对管脚进行分配

使用菜单 Assignments -> Device -> Device and Pin Options 配置工程

生成pof文件: 在 Configuration中钩选"Use configuration device", 并选择"EPCS128", 当然对于A4来说没用, 因为这块开发板上没留AS下载口;

未使用管脚: 在Unused Pins选择"As input tri-stated", 其实默认的"As input tri-stated with weak pull-up"好像更好, 只是功耗会稍微大一点点吧

双用的管脚因开发板全引为用户IO, 所以在Dual-Purpose Pins中全部选择"Use as regular I/O"

双击下左边的Compile Design", 完成后生成sof, pof文件

菜单 Tools -> Programmer, 下载程序, 当然得有USB-Blaster

点Start开始下载, 速度飞快, 因为是下到RAM, 断电后就没了, 没有AS接口, 所以pof文件没用, 要写到ROM, 用另一个方法

菜单 File -> Convert Programming Files, "Programming file type"选择"JTAG Indirect Configuration File(.jic)"

"configuration device", 选择"EPCS128"

下面的Flash Loader选择 Add Device: Cylone IV E -> EP4CE10;

SOF Data选择 Add File: decode4_7.sof

菜单 Tools -> Programmer, Add File: output_file.jic, 勾选"Program/Configure", 点Star下载程序, 速度有蛮慢

四. 最后

最后附上不能正常测试的仿真文件, 和工程工作视频载图

二楼被吃了

然后多发了两次

二楼被吃了

一周热门 更多>