最近在做课题的时候遇到FIR滤波器,我就用ISE自带的IP核完成了,但是输出并没有滤波是怎么回事呢?

比如我设计的滤波器为50Hz的低通滤波器,在MATLAB里面获得系数并且归一化为整型,将系数搞了进去,完成了IP核例化。

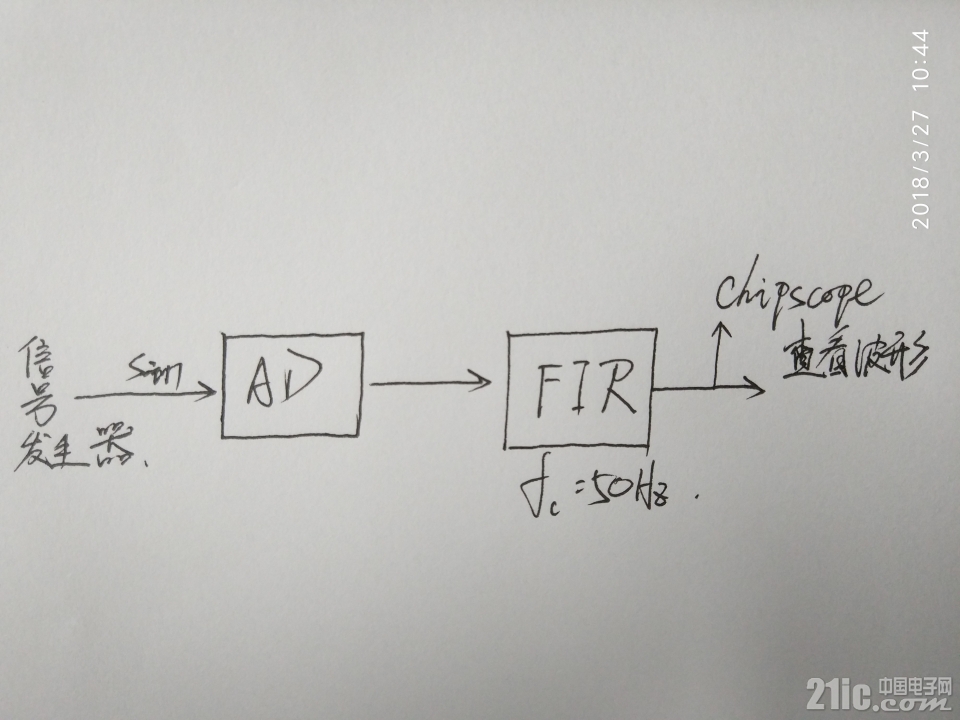

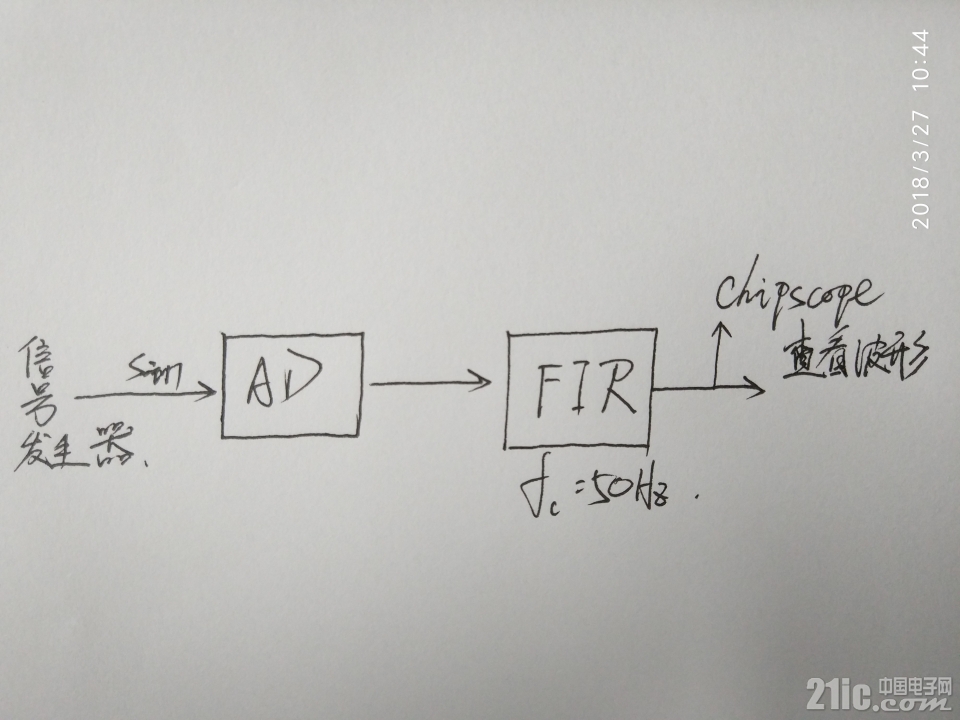

同时,滤波器前一级为A/D电路,这个是调通的,没问题。整个电路结构如下图

在测试输出的时候用信号发生器作为信号源,经A/D转化后进入滤波器,输入为50kHz,但是我通过Chipscope查看滤波器输出,发现并不能滤波,只是将波形放大而已。

这是怎么回事呢?我猜想是由于系数归一化的时候进行了放大导致输出也变大,不知对不对呢?

有点想不明白。请指点

比如我设计的滤波器为50Hz的低通滤波器,在MATLAB里面获得系数并且归一化为整型,将系数搞了进去,完成了IP核例化。

同时,滤波器前一级为A/D电路,这个是调通的,没问题。整个电路结构如下图

在测试输出的时候用信号发生器作为信号源,经A/D转化后进入滤波器,输入为50kHz,但是我通过Chipscope查看滤波器输出,发现并不能滤波,只是将波形放大而已。

这是怎么回事呢?我猜想是由于系数归一化的时候进行了放大导致输出也变大,不知对不对呢?

有点想不明白。请指点

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

可是A/D我事先调过,是通的

再将matlab的系数转为fpga内部参量,用chipscope看滤波后的效果

一周热门 更多>