勇敢的芯伴你玩转Altera FPGA连载55:蜂鸣器开关实例特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

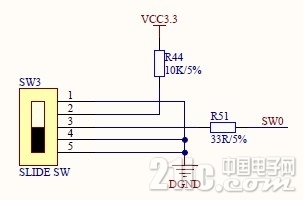

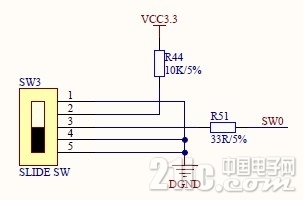

我们已经在上一章的例程中,知道了蜂鸣器工作的基本原理,即FPGA输出高电平就发出响声,FPGA输出低电平就停止发声。在本节中,我们增加一个拨码开关做控制,让拨码开关的ON或OFF状态相应的去控制蜂鸣器的发声与不发声。 拨码开关SW3的电路如图8.1所示。拨码开关与FPGA相连接的SW0信号的电平值取决于拨码开关当前的位置,若它连接了2-3脚,那么SW0就是高电平状态,若它连接了3-4脚,就是低电平状态。

图8.1 拨码开关电路 如图8.2所示,每一个拨码开关的右侧都有“ON”和“OFF”的丝印标示。“ON”对应的是3-4脚连接状态,“OFF”对应的是2-3脚连接状态。

图8.2 拨码开关实物照片 综上所述,也就是当拨码开关处于“ON”状态时,SW0输出低电平;当拨码开关处于“OFF”状态时,SW0输出高电平。 而我们要实现的功能是,当拨码开关处于“ON”状态时,蜂鸣器发声;当拨码开关处于“OFF”状态时,蜂鸣器不发声。 本实例的工程代码如下,只有cy4.v一个Verilog源文件。module cy4( input ext_clk_25m, //外部输入25MHz时钟信号 input ext_rst_n, //外部输入复位信号,低电平有效 input[0:0] switch, //拨码开关SW3输入,ON -- 低电平;OFF-- 高电平 output reg beep //蜂鸣器控制信号,1--响,0--不响 ); //------------------------------------- //蜂鸣器发声控制always @ (posedge ext_clk_25m or negedge ext_rst_n) if(!ext_rst_n) beep <= 1'b0; else if(!switch[0]) beep <=1'b1; //蜂鸣器响 else beep <= 1'b0; //蜂鸣器不响 endmodule 这段代码中,ext_rst_n是复位信号,当它为低电平的时候,也就是复位按键被按下的时候,beep信号为低电平,即蜂鸣器不发声。而当ext_rst_n为高电平的时候,也就是系统正常运行时,蜂鸣器控制信号beep的高低电平状态则由拨码开关switch[0]决定,即由拨码开关SW3的状态决定。当SW3处于ON状态(低电平)时,蜂鸣器发声;当SW3处于OFF状态(高电平)时,蜂鸣器不发声。

一周热门 更多>