勇敢的芯伴你玩转Altera FPGA连载48:PWM蜂鸣器驱动之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

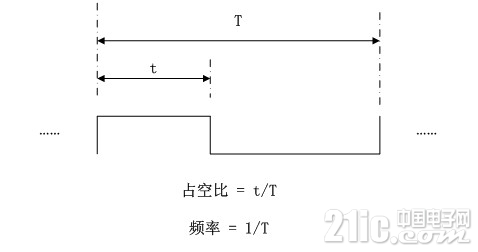

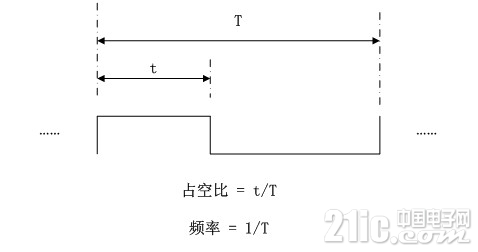

蜂鸣器是一种最简单的发声元器件,它的应用也非常广泛,大都是作为报警或发声提醒装置。比如我们家里的电脑在刚开启时,通常主板上会发出一声较短的尖锐的“滴……”的鸣叫声,提示用户主板自检通过,可以正常进行后面的启动;而如果是1长1短或1长2短的鸣叫声,则表示可能发生了电脑内存或显卡故障;当然还可以有其他不同的鸣叫声提示其他的故障,总而言之,可别小看了这颗区区几毛钱的小家伙,关键时刻还挺有用的。可以毫不夸张的说,蜂鸣器也算是一种人机交互的手段。PWM(Pulse Width Modulation),即脉冲宽度调制,如图7.1所示,PWM的输出只有高电平1和低电平0。PWM不停的重复输出周期为T,其中高电平1时间为t的脉冲,t/T是它的占空比,1/T是它的频率。

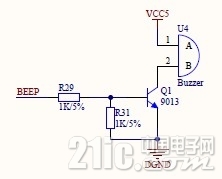

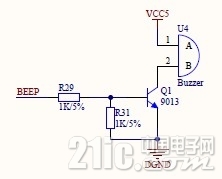

图7.1 PWM信号如图7.2所示,这是SP6板上蜂鸣器的电路原理图,BEEP网络连接到FPGA的IO上,当BEEP = 1时,三极管Q1的BE导通,则CE也导通,那么U4的2端直接接地,因此在它两端有5V的电压,那么蜂鸣器就发声了。同理,BEEP =0时,Q1截止,U4的2端相当于开路,则蜂鸣器不会发出声音。

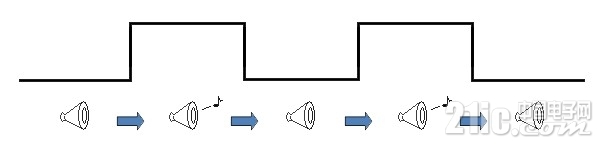

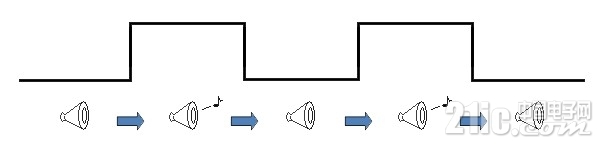

图7.2 蜂鸣器电路 如图7.3所示,基于蜂鸣器在FPGA的IO输出1就发声、0则不发声的原理,我们给IO口一个占空比为50%的PWM的信号,让蜂鸣器间歇性的发声鸣叫。如果它的频率高则发声就显得相对尖锐急促一些,如果它的发声频率低则发声就显得低沉平缓一些。

图7.3 蜂鸣器与PWM发声映射 在我们给出的实例代码中,我们期望产生一个输出频率为25Hz(40ms)、占空比为50%的PWM信号去驱动蜂鸣器的发声。因此,我们使用系统时钟25MHz(40ns)进行计数,每计数1,000,000次,这个计数器就清零重新计算。因为这个计数器是2进制的,要能够表达0-999999的任意一个计数值,那么这个2进制计数器至少必须是20位的。此外,为了得到输出的PWM占空比为50%,那么我们只要判断计数值小于最大计数值的一半即500000时,输出高电平1,反之输出低电平0。

一周热门 更多>