勇敢的芯伴你玩转Altera FPGA连载45:基于仿真的第一个工程实例之测试脚本创建与编辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

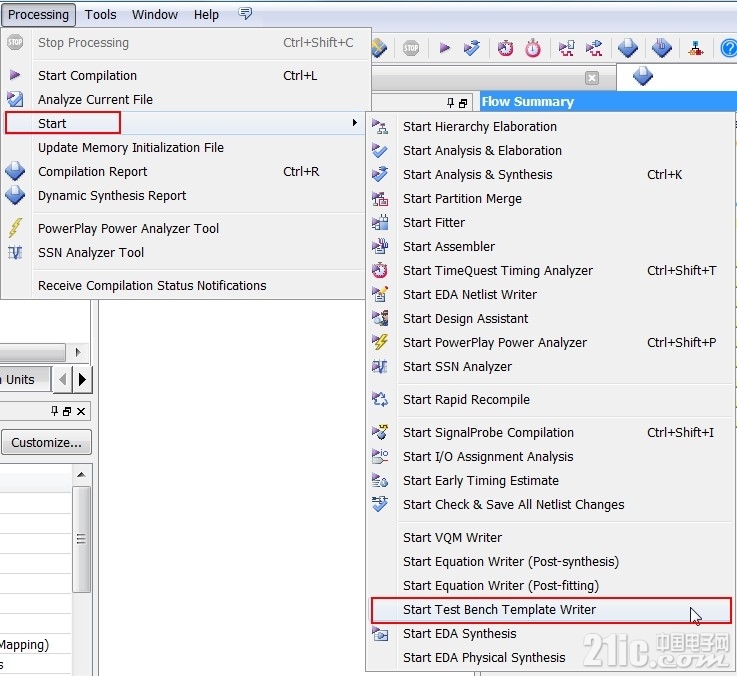

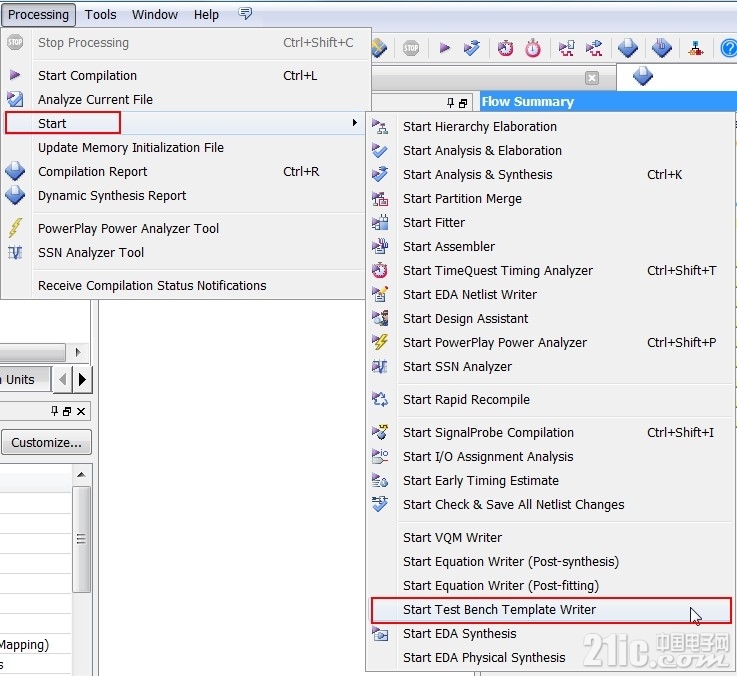

回到Quartus II工具中,如图6.13所示,点击菜单栏的“ProcessingàStartàStart Test Bench Template Writer”,随后弹出提示“Test Bench Template Writer was successful”(在此之前,最好对整个工程做一次全编译,否则可能报错),那么我们就已经创建了一个Verilog测试脚本,在此脚本中,我们可以设计一些测试激励输入并且观察相应输出,借此我们就能够验证原工程的设计代码是否符合要求。

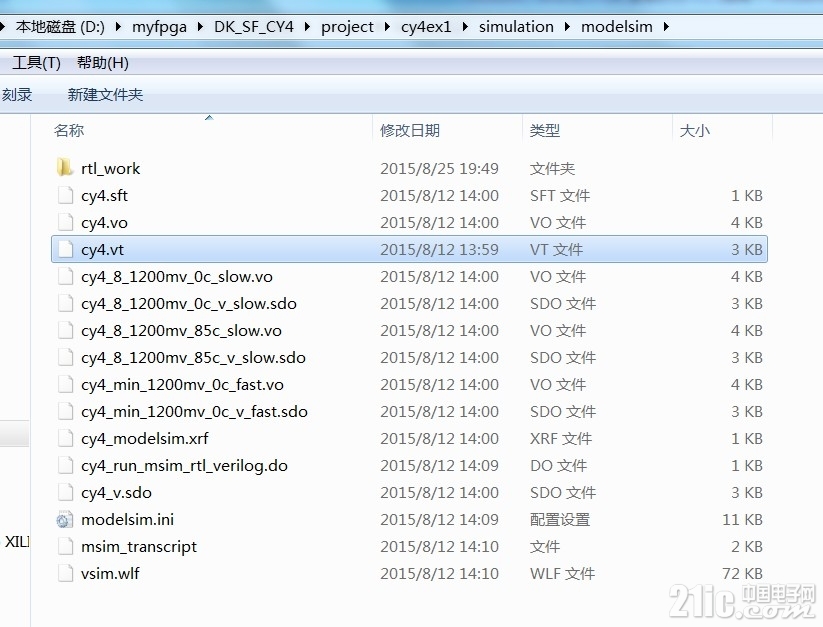

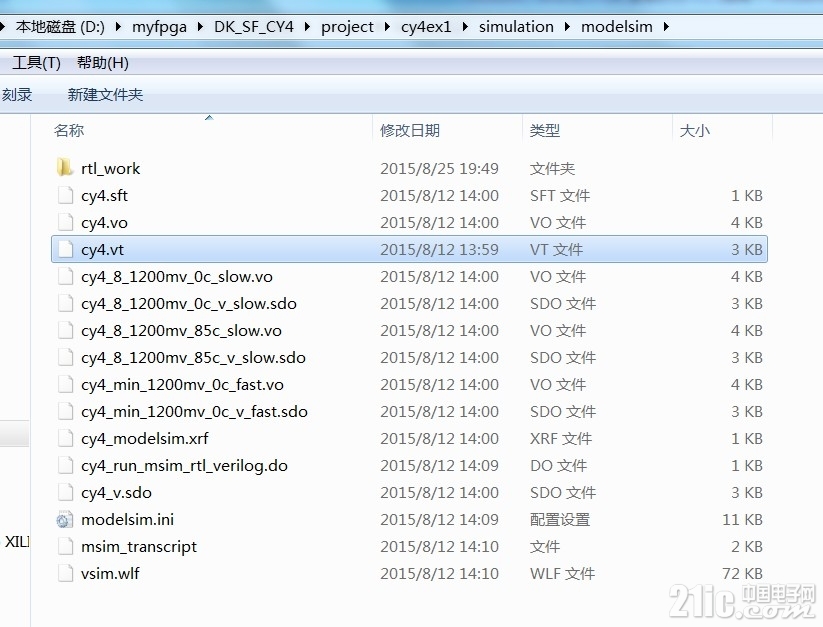

图6.13 生成测试脚本 我们打开工程所在文件夹下的“…/simulation/modelsim”文件夹,如图6.14所示,可以看到一个名为cy4.vt的测试脚本文件创建好了。

图6.14 测试脚本文件 测试脚本文件在Notepad++中打开了。这里的测试脚本只是一个基本的模板,它把设计文件cy4.v的接口在这个模块里面例化申明了,我们还需要自动动手添加复位和时钟的激励,编辑好的测试脚本如下所示。`timescale 1 ns/ 1 psmodule cy4_vlg_tst(); // test vector input registersreg ext_clk_25m;reg ext_rst_n; // wires wire clk_12m5; // assign statements (if any) cy4 i1 (// port map - connection between master ports and signals/registers .clk_12m5(clk_12m5), .ext_clk_25m(ext_clk_25m), .ext_rst_n(ext_rst_n)); initial begin // Initialize Inputs ext_clk_25m = 0; ext_rst_n = 0; // Wait 100 ns for globalreset to finish #100; ext_rst_n = 1; // Add stimulus here #2000; $stop; end always #20 ext_clk_25m =~ext_clk_25m; //产生25MHz时钟源 endmodule 有朋友可能是第一次接触测试仿真,关于仿真的基本概念请查看《FPGA设计实战演练(逻辑篇)》第九章的设计仿真部分内容。

一周热门 更多>