勇敢的芯伴你玩转Altera FPGA连载42:基于仿真的第一个工程实例之Verilog源码文件编辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

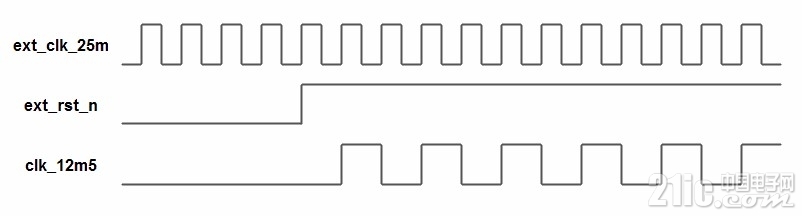

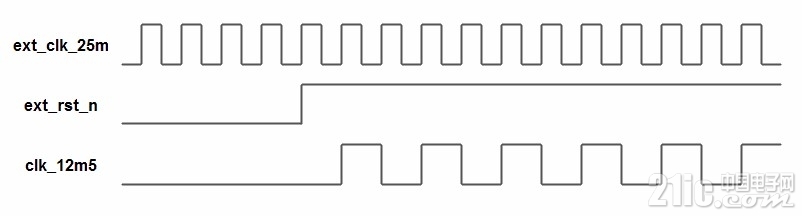

我们接着在该文件中输入实现实验功能的一段Verilog代码如下。//对外部输入时钟做二分频module cy4( input ext_clk_25m, //外部输入25MHz时钟信号 input ext_rst_n, //外部输入复位信号,低电平有效 output reg clk_12m5 //二分频时钟信号 ); always @(posedge ext_clk_25m or negedge ext_rst_n) if(!ext_rst_n) clk_12m5 <=1'b0; else clk_12m5 <= ~clk_12m5; endmodule 这段代码的功能是:● 输入复位信号ext_rst_n为低电平时,即复位状态。无论输入时钟ext_clk_25m是否运行,输出信号clk_12m5始终保持低电平。● 输入复位信号ext_rst_n为高电平时,即退出复位。每个ext_clk_25m时钟信号的上升沿,信号clk_12m5的输出值翻转。如图5.14所示,这便是前面的代码将要实现的功能。

图6.7 源码实现功能波形

一周热门 更多>