勇敢的芯伴你玩转Altera FPGA连载28: 内里本质探索——器件结构 下特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

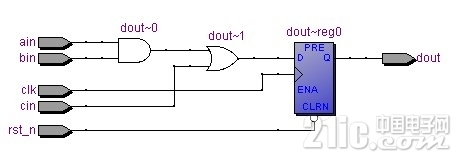

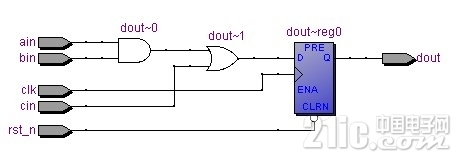

说了这么多理论,估计大伙都有些头大了。下面举个例子,让大家看看一个简单的逻辑功能是如何用这个正常模式下的LEs来实现的。有如下一段Verilog代码:module ex0( clk,rst_n, ain,bin,cin,dout ); input clk;input rst_n;input ain,bin,cin;output reg dout; always @(posedge clk or negedge rst_n) if(!rst_n) dout <= 1'b0; else dout <= (ain & bin) |cin; endmodule 看不懂不要紧,咱还没开始学语法呢。这个电路中,输入信号ain、bin和cin,复位信号rst_n,时钟信号clk,输出信号dout。输出信号dout在复位信号rst_n有效时输出为0,在撤销复位(rst_n = 1)后每个时钟上升沿锁存当前的最新值,这个最新值为当前输入信号ain与bin再或cin的结果。其逻辑功能如图3.24所示,是一个典型的时序逻辑,这个电路中有我们前面提到的与门、或门和寄存器等基本组件。

图3.24 逻辑功能视图 再看经过Quartus II工具的“翻译”后,如图3.25所示,前面这段逻辑被映射到了Cyclone IV的LEs中。和图3.23相比较,可以确认这是LEs的正常模式,图中高亮部分是被“编程”开启功能的电路实现。不要感到稀奇,这个原本要实现与门、或门等逻辑功能的电路却不是用与门、或门来实现的,而是我们前面提到的LUT在这里扮演了很重要的角 {MOD}。有人可能又要纳闷了LUT到底为何物?有那么神通广大么?别说,还真那么回事。就拿4输入的LUT来说,其实它里面就相当于一个16bit的存储器,或者你也可以理解LUT里面存放着4个输入信号的真值表,输入信号通过这个真值表便可得到期望的结果,就如我们这个实例一样。

图3.25 LEs中的逻辑实现

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

而赛灵思的fpga是门阵列

一周热门 更多>