勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

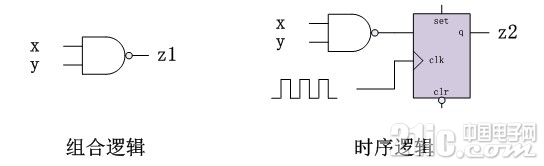

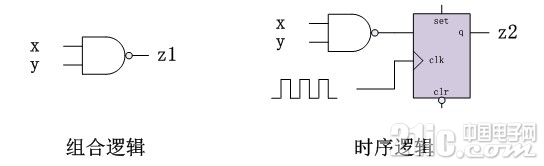

数字电路按照逻辑功能一般可以分为组合逻辑和时序逻辑。组合逻辑不含有任何用于存储比特信号的电路,它的输出只和当前电路的输入有关,如前面(图3.12)所列举的加法器的电路。时序逻辑可以含有组合逻辑,并且一定有用于存储比特信号的电路(一般为寄存器),时序逻辑的输出值不仅和当前输入值有关,一般也和电路的原有状态相关。 如图3.16所示,同样是简单的与非门电路,左侧为组合逻辑,右侧则为时序逻辑。

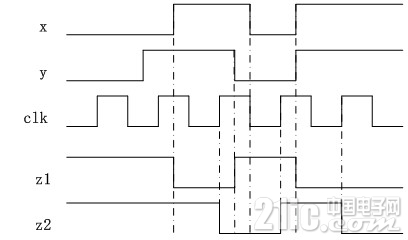

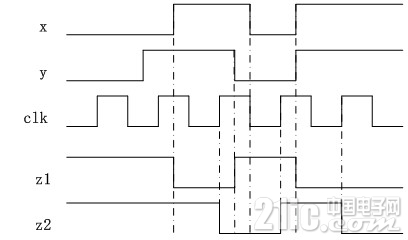

图3.16 组合逻辑与时序逻辑电路 如图3.17所示,以上面的组合逻辑和时序逻辑电路为例,输入信号x和y为随机信号,组合逻辑的输出信号z1在输入x和y发生变化并满足逻辑变化条件时立刻发生变化,当然了,这个变化在实际电路中也有一定的延时。而在时序逻辑中,该实例除了组合逻辑满足条件外,只有在时钟信号clk的每个上升沿输出z2才会发生变化。这里有一个细节大家也需要注意,x和y的组合逻辑输出值在时钟上升沿到来的前后的某段时间内(即建立时间和保持时间)必须是稳定的,否则有可能锁存到不稳定的值(即亚稳态)。

图3.17 波形输入与输出示例 通过这个简单的例子,我们大致可以了解组合逻辑和时序逻辑的特点。一般而言,他们存在以下的区别:● 组合逻辑的输出与输入直接相关,时序逻辑的输出和原有状态也有关。● 组合逻辑立即反应当前输入状态,时序逻辑还必须在时钟上升沿触发后输出新值。● 组合逻辑容易出现竞争、冒险现象,时序逻辑一般不会出现。● 组合逻辑的时序较难保证,时序逻辑更容易达到时序收敛。● 组合逻辑只适合简单的电路,时序逻辑能够胜任大规模的逻辑电路。在今天的数字系统应用中,纯粹用组合逻辑来实现一个复杂功能的应用几乎绝迹了。时序逻辑在时钟驱动下,能够按部就班的完成各种复杂的任务,也能够非常便利的达到时序要求,并且能够解决各种异步处理带来的亚稳态问题。因此,时序逻辑设计的一些方法和手段是大家必须掌握和熟练应用的。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>