例说FPGA连载96:基于HDMI的AV采集显示之Verilog代码解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

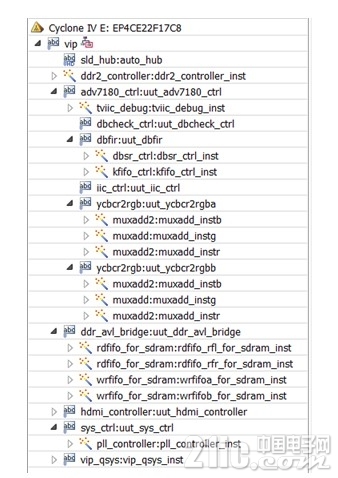

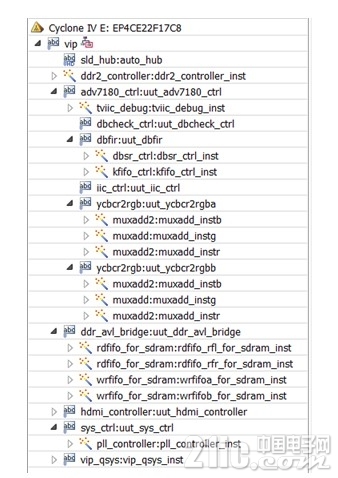

本实例分为4个层级,大大小小共计25个模块,其层次结构如图19.4所示。

图19.4 工程实例17代码层次图 各个模块的功能描述如表19.1所示。表19.1 代码模块功能描述 模块名 功能描述vip.v该模块是顶层模块,其下例化了6个子模块。该模块仅仅用于子模块间的接口连接,以及和FPGA外部的接口定义,该模块中未作任何的逻辑处理。ddr2_controller.v该模块是一个软核IP,实现DDR2的时序控制功能,并且通过一个简单的Avalon接口实现DDR2和FPGA逻辑之间的读写数据传输。ddr_avl_bridge.v该模块作为连接ddr2_controller的桥接模块,用户逻辑中要写入或读出DDR2的数据都需要通过该模块例化的DDR2读数据缓存FIFO或DDR2写数据缓存FIFO实现。rdfifo_for_sdram.v 该模块为片内存储器例化的FIFO,用于缓存从DDR2读出的数据。wrfifo_for_sdram.v 该模块为片内存储器例化的FIFO,用于缓寸写入DDR2的数据。hdmi_controller.v该模块产生480p/600p/768p/960p/1024p/1080p分辨率可调的HDMI接口显示驱动逻辑,同时该模块也产生DDR2读操作接口的控制信号。sys_ctrl.v该模块中例化了PLL模块,并且对输入PLL的复位信号以及PLL锁定后的复位信号进行“异步复位,同步释放”的处理,确保系统的复位信号稳定可靠。pll_controller.v 该模块为FPGA器件特有的IP硬核模块,其主要功能是产生多个特定输入时钟的分频、倍频、相位调整后的输出时钟信号。adv7180_ctrl.v该模块包含6个子模块,实现对ADV7180芯片的IIC寄存器初始化以及ITU656格式AV视频信号的采集、协议解析、去隔行处理、YCrCb转RGB处理等功能。iic_ctrl.v 该模块产生IIC的读写时序,实现对ADV7180芯片的IIC接口寄存器访问。tiic_debug.v 例化的“In-System Sources and Probes Editor”IP核,可用于在线访问IIC寄存器。dbcheck_ctrl.v ITU656协议的AV视频流解码,去除协议的帧头和帧尾,提取出有效的视频数据。dbfir.v 使用移位寄存器和FIFO,对视频流缓存并实现去隔行处理。dbsr_ctrl.v 移位寄存器,用于缓存一行的视频图像。kfifo_ctrl.v 该模块的FIFO用于缓存ITU656协议解码后的有效视频数据流。ycbcr2rgb.v 将YCrCb格式输入的视频流转换为RGB格式输出的视频流。muxadd.v 3路输入的乘累加IP核。Muxadd2.v 2路输入的乘累加IP核。vip_qsys.v该模块是Qsys系统的例化,该模块例化了一个NIOS II处理器,作为Avalon-MM总线的主机;Avalon-MM总线上可访问的从机有片内RAM、System ID、JTAG UART、HDMI_MODE_PIO、LED_PIO、Timer以及自定义的IIC控制器组件。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>