勇敢的芯伴你玩转Altera FPGA连载11:关于FPGA器件的时钟特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

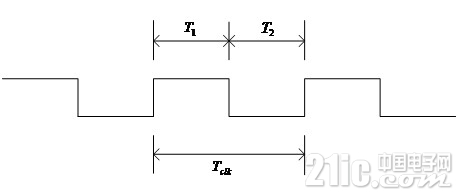

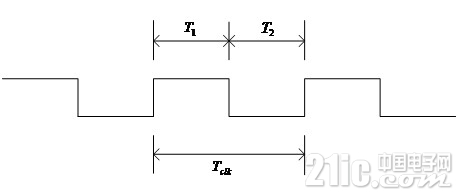

如图2.7所示,理想的时钟模型是一个占空比为50%且周期固定的方波。file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image004.gif为一个时钟周期,file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image006.gif为高脉冲宽度,file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image008.gif为低脉冲宽度,file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image004.gif=file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image006.gif+file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image008.gif。一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后输出最终的运算结果。时钟信号的引入,不仅让所有的数字运算过程变成“可量化”的,而且也能够将各种不相关的操作过程同步到一个节拍上协同工作。

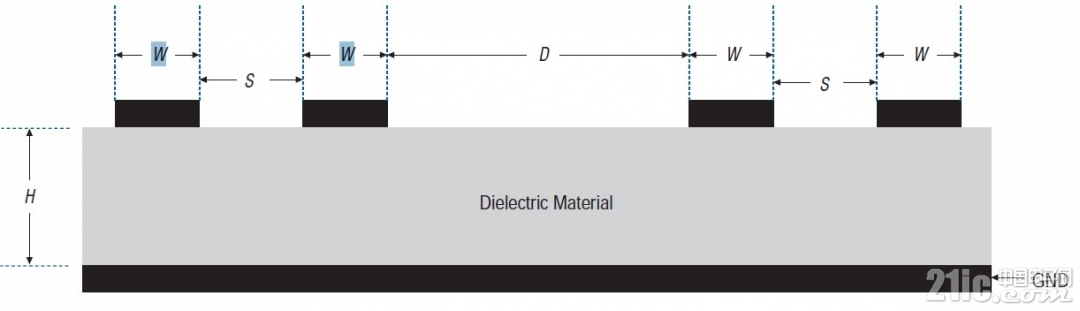

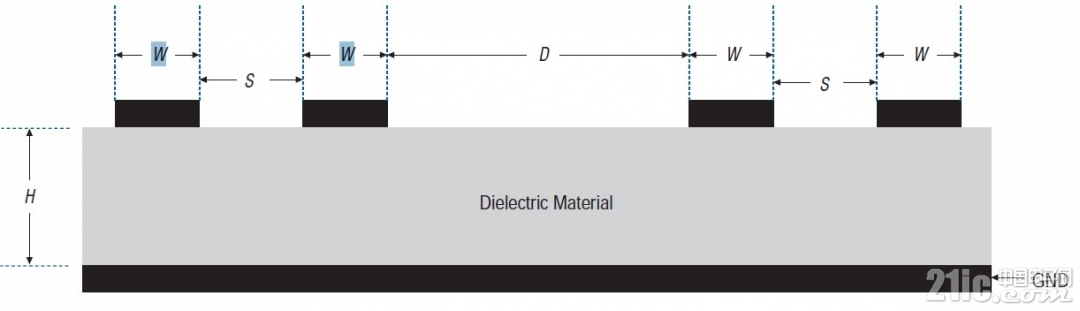

图2.7 理想时钟波形FPGA器件的时钟信号源一般来自外部,我们通常使用晶体振荡器(简称晶振)产生时钟信号。当然了,一些规模较大的FPGA器件内部都会有可以对时钟信号进行倍频或分频的专用时钟管理模块,如PLL或DLL。由于FPGA器件内部使用的时钟信号往往不只是供给单个寄存器使用,因为在实际应用中,成百上千甚至更多的寄存器很可能共用一个时钟源,那么从时钟源到不同寄存器间的延时也可能存在较大偏差(我们通常称为时钟网络延时),而我们知道,这个时间差过大是很要命的。因此,FPGA器件内部设计了一些称之为“全局时钟网络”的走线池。通过这种专用时钟网络走线,同一时钟到达不同寄存器的时间差可以被控制到很小的范围内。而我们又如何能保证输入的时钟信号能够走“全局时钟网络”呢?有多种方式,对于外部输入的时钟信号,只要将晶振产生的时钟信号连接到“全局时钟专用引脚”上;而对于FPGA内部的高扇出控制信号,通常工具软件会自动识别此类信号,将其默认连接到“全局时钟网络”上,而设计者若是不放心,也可通过编译报告进行查看,甚至可以手动添加这类信号。关于时钟电路的设计和选型,有如下几个基本事项需要考虑:● 系统运行的时钟频率是多少?(可能有多个时钟)● 是否有内部的时钟管理单元可用(通常是有)?它的输入频率范围(需要查看器件手册进行确认)?● 尽可能选择专用的时钟输入引脚。关于FPGA时钟电路的PCBLayout设计,通常需要遵循以下的原则。● 时钟晶振源应该尽可能放在与其连接的FPGA时钟专用引脚的临近位置。● 时钟线尽可能走直线。如果无法避免转弯走线,使用45度线,尽量避免T型走线和直角走线。● 不用同时在多个信号层走时钟线。● 时钟走线不要使用过孔,因为过孔会导致阻抗变化及反射。● 靠近外层的地层能够最小化噪声。如果使用内层走时钟线,要有良好的参考平面,且走带状线。● 时钟信号应该有终端匹配电路,以最小化反射。● 尽可能使用点到点的时钟走线。● 如图2.8所示,对于时钟差分对的走线,必须严格按照D>2S规则,以最小化相邻差分对间的串扰。

图2.8 时钟差分对的间隔● 确保整个差分对在整个走线过程中的线间距恒定。● 确保差分对的走线等长,以最小化偏斜和相移。● 同一网络走线过程中避免使用多个过孔,以确保阻抗匹配和更低的感抗。● 高频的时钟和USB差分信号对走线尽可能短。● 高频时钟或周期性信号尽可能远离高速差分对以及任何引出的连接器(例如I/O连接器、控制和数据连接器或电源连接器)。● 应当保证所有走线有持续的地和电源参考平面。● 为了最小化串扰,尽量缩短高频时钟或周期性信号与高速信号并行走线的长度。推荐的最小间距是3倍的时钟信号与最近参考面间距。● 当一个时钟驱动多个负载时,使用低阻抗传输线以确保信号通过传输线。● 信号换层时使用回路过孔。同步时钟的延时应该与数据相匹配。确保时钟与同步数据总线在同一层走线,以最小化不同层之间的传输速率差异。

一周热门 更多>