本帖最后由 ucx 于 2017-10-18 15:22 编辑

时钟问题是FPGA代码要考虑的首要问题,决定了系统的稳定性和健壮性。时钟问题的讨论,从一个最简单的实例开始。

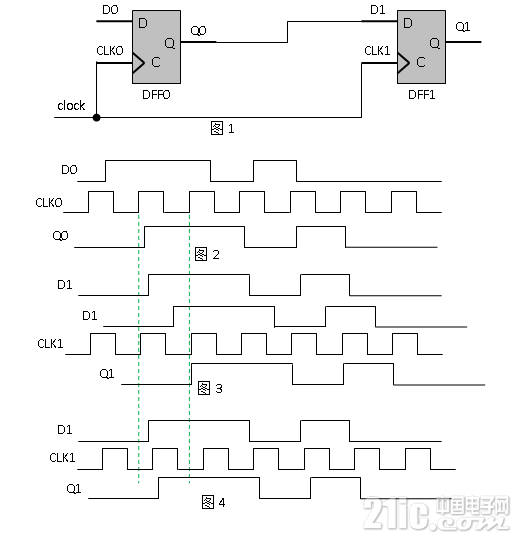

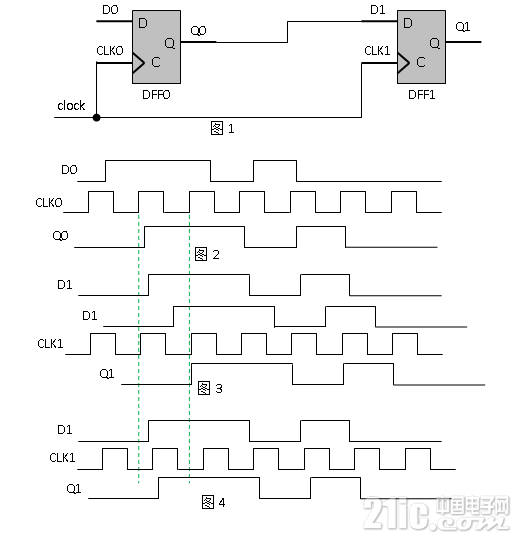

一段简单VHDL代码,一个简单的实例,用来实现Q1相对于Q0延时一个时钟周期:Process(clock) begin if rising_edge(clock)then Q0 <= D0; Q1 <= Q0; end if;End process;这段代码,实际上代表着图1所示电路。电路使用了两个D触发器DFF0和DFF1。时钟clock经时钟布线资源到两个触发器时钟输入端,成为两个触发器真正使用的时钟CLK0和CLK1。数据D0连接到DFF0的数据输入端,Q0为DFF0的输出。Q0经内部数据布线资源达到DFF1数据输入端成为信号D1,最后D1被CLK1锁存到Q1。目前看起来,这些表述是不是像饶舌的废话?

图2展示了DDF0的输入与输出的时序关系,图中标明Q0相对于CLK0上升沿有微小延时。如果clock是经全局时钟网络到达CLK0和CLK1,那么FPGA的时钟布线资源保证了CLK0和CLK1在时序上几乎完全重合,在图3中以CLK1相对于CLK0有极微小时延来表示。而Q0到D1的延时随Q0到D1的组合逻辑不同延时有很大差别。实例中,只是以简单的直通逻辑表示。图3标明只要Q0到D1的延时不小于时钟线延时且不超过一个时钟周期,那么Q1输出总是滞后Q0一个时钟周期,逻辑工作正常。当实际逻辑复杂时,比如Q0和D1代表8根数据线,这8根线的组合逻辑各不相同。此时如果保证逻辑正常,那么clock的一个时钟周期必须大于最大时延与最小时延的时间差。clock的最小周期要求就决定了clock的最高工作速率。

现在假设,clock没有布线到时钟网络,而是占用的数据布线资源。则有可能出现CLK0到CLK1延时大于Q0到D1延时的情况,时序如图4所示。那么Q1并没有像期望的那样延时一个时钟周期,发生了逻辑错误。

图4的错误告诉我们时钟信号应优先选用时钟布线资源。而时钟网络资源相对于数据布线资源来说是有限的,并且能够进入时钟网络的信号或管脚也是有条件的,是受限的。这要求我们在书写代码的时候不能随便拿来一个信号就用作时钟,FPGA的时钟资源也决定了不能够实现过多的信号进入时钟网络。最理想的情况是整个系统使用同一个时钟信号,也就是我们常听说的全同步系统。另外,也常见一些FPGA工程师在使用时钟的时候总是在一个模块上升沿输出,到另一个模块时用下降沿读取。这是早期使用分离器件搭建数字电路遗留下来的习惯,在FPGA内使用这一方法有欠妥当。比如图2中Q0到D1延时超过半个周期时,工作逻辑出错。双沿交替使用使最高时钟频率下降一半。FPGA的时钟网络保证了,上升沿输出的数据信号在延时不超过一个时钟周期的条件下,继续用上升沿读取不会发生错误。

一个全同步系统,只要实际工作时钟频率不超过代码综合后报告的最高频率,工作总是稳定的,这是最重要的,也是每个FPGA工程师所期望的。另外,全同步系统也避免出现因时钟延时不满足而出现的各种奇怪貌似无法解释的现象,极大地降低了调试的工作量。实际应用系统中的FPGA常常有很多接口,比如SRAM、高速光路信号、USB、硬盘等高速接口以及I2C、SPI、UART和键盘鼠标等低速接口,它们均有各自的时钟。面对这些林林总总,如何把FPGA打造成全同步系统呢?跨时钟域的数据如何处理呢?全同步系统设计有哪些注意事项呢?限于帖子的字数要求,这些问题留在下一帖再作讨论。

一句话,时钟是关键,全同步设计是目标。

时钟问题是FPGA代码要考虑的首要问题,决定了系统的稳定性和健壮性。时钟问题的讨论,从一个最简单的实例开始。

图2展示了DDF0的输入与输出的时序关系,图中标明Q0相对于CLK0上升沿有微小延时。如果clock是经全局时钟网络到达CLK0和CLK1,那么FPGA的时钟布线资源保证了CLK0和CLK1在时序上几乎完全重合,在图3中以CLK1相对于CLK0有极微小时延来表示。而Q0到D1的延时随Q0到D1的组合逻辑不同延时有很大差别。实例中,只是以简单的直通逻辑表示。图3标明只要Q0到D1的延时不小于时钟线延时且不超过一个时钟周期,那么Q1输出总是滞后Q0一个时钟周期,逻辑工作正常。当实际逻辑复杂时,比如Q0和D1代表8根数据线,这8根线的组合逻辑各不相同。此时如果保证逻辑正常,那么clock的一个时钟周期必须大于最大时延与最小时延的时间差。clock的最小周期要求就决定了clock的最高工作速率。

现在假设,clock没有布线到时钟网络,而是占用的数据布线资源。则有可能出现CLK0到CLK1延时大于Q0到D1延时的情况,时序如图4所示。那么Q1并没有像期望的那样延时一个时钟周期,发生了逻辑错误。

图4的错误告诉我们时钟信号应优先选用时钟布线资源。而时钟网络资源相对于数据布线资源来说是有限的,并且能够进入时钟网络的信号或管脚也是有条件的,是受限的。这要求我们在书写代码的时候不能随便拿来一个信号就用作时钟,FPGA的时钟资源也决定了不能够实现过多的信号进入时钟网络。最理想的情况是整个系统使用同一个时钟信号,也就是我们常听说的全同步系统。另外,也常见一些FPGA工程师在使用时钟的时候总是在一个模块上升沿输出,到另一个模块时用下降沿读取。这是早期使用分离器件搭建数字电路遗留下来的习惯,在FPGA内使用这一方法有欠妥当。比如图2中Q0到D1延时超过半个周期时,工作逻辑出错。双沿交替使用使最高时钟频率下降一半。FPGA的时钟网络保证了,上升沿输出的数据信号在延时不超过一个时钟周期的条件下,继续用上升沿读取不会发生错误。

一个全同步系统,只要实际工作时钟频率不超过代码综合后报告的最高频率,工作总是稳定的,这是最重要的,也是每个FPGA工程师所期望的。另外,全同步系统也避免出现因时钟延时不满足而出现的各种奇怪貌似无法解释的现象,极大地降低了调试的工作量。实际应用系统中的FPGA常常有很多接口,比如SRAM、高速光路信号、USB、硬盘等高速接口以及I2C、SPI、UART和键盘鼠标等低速接口,它们均有各自的时钟。面对这些林林总总,如何把FPGA打造成全同步系统呢?跨时钟域的数据如何处理呢?全同步系统设计有哪些注意事项呢?限于帖子的字数要求,这些问题留在下一帖再作讨论。

一句话,时钟是关键,全同步设计是目标。

一周热门 更多>