大家好,请教一个问题。

首先,背景是我用VHDL编程经验并不多,现在写了一个组合逻辑的比较器,代码如下:

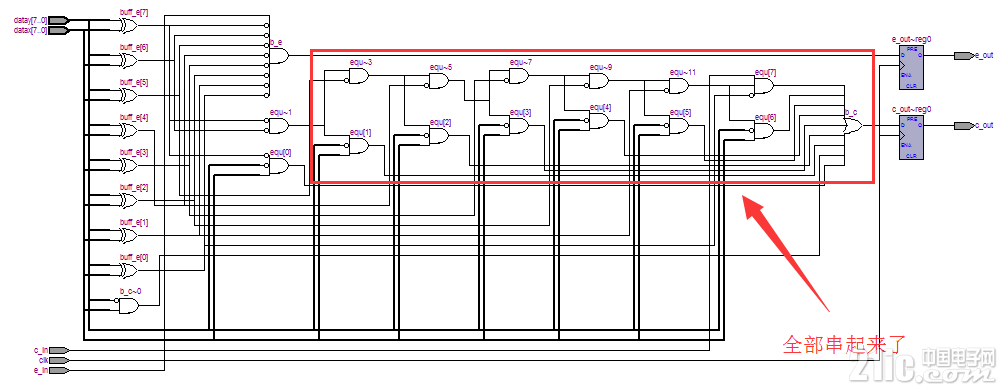

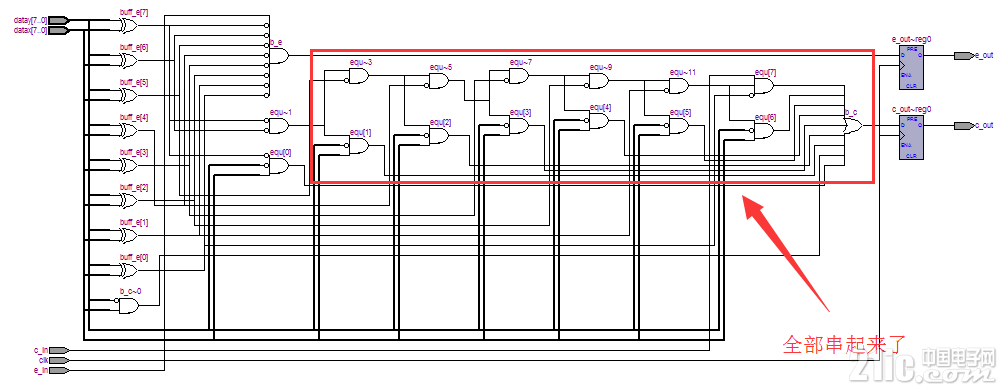

但是,生成的RTL电路结构并非我想要的形式,实际生成的RTL电路采用了多级级联的与方式,这样导致了仿真出现很多毛刺,RTL 电路如下图:

我的想法是这些逻辑与门应该是多输入的方式存在,而非级联,就算浪费点,速度也不会太慢。

想请教大家的是,我该如何做呢?或是如何设置呢?

首先,背景是我用VHDL编程经验并不多,现在写了一个组合逻辑的比较器,代码如下:

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- USE IEEE.STD_LOGIC_ARITH.ALL;

- ENTITY com_8 IS

- PORT

- (

- datax : in std_logic_vector(7 downto 0); --比较数据x

- datay : in std_logic_vector(7 downto 0); --比较数据y

- c_out : out std_logic; --比较结果,x>y 输出1,否则输出0

- e_out : out std_logic; --比较结果,x=y 输出1,否则输出0

- c_in : in std_logic; --比较结果输入,用于级联 --大于

- e_in : in std_logic; --比较结构输入,用于级联 --相等

- --clk : in std_logic

- );

- END com_8;

- ARCHITECTURE behavior OF com_8 IS

- signal b_c, b_e : std_logic;

- signal buff_e : std_logic_vector(7 downto 0);

- signal equ : std_logic_vector(7 downto 0);

- BEGIN

- process(clk)

- begin

- if(clk'event and clk='1') then

- e_out <= b_e;

- c_out <= b_c;

- end if;

-

- end process;

-

- buff_e(0) <= datax(0) xnor datay(0);

- buff_e(1) <= datax(1) xnor datay(1);

- buff_e(2) <= datax(2) xnor datay(2);

- buff_e(3) <= datax(3) xnor datay(3);

- buff_e(4) <= datax(4) xnor datay(4);

- buff_e(5) <= datax(5) xnor datay(5);

- buff_e(6) <= datax(6) xnor datay(6);

- buff_e(7) <= datax(7) xnor datay(7);

-

-

- -- equ(0) <= (buff_e(7) and (datax(6) and(not datay(6))));

- -- equ(1) <= (buff_e(7) and buff_e(6) and (datax(5) and(not datay(5))));

- -- equ(2) <= (buff_e(7) and buff_e(6) and buff_e(5) and (datax(4) and(not datay(4))));

- -- equ(3) <= (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and (datax(3) and(not datay(3))));

- -- equ(4) <= (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and (datax(2) and(not datay(2))));

- -- equ(5) <= (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and (datax(1)and(not datay(1))));

- -- equ(6) <= (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and buff_e(1) and (datax(0)and(not datay(0))));

- -- equ(7) <= (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and buff_e(1) and buff_e(0) and c_in);

-

- b_e <= buff_e(0) and buff_e(1) and buff_e(2) and buff_e(3) and buff_e(4) and buff_e(5) and buff_e(6) and buff_e(7) and e_in;

-

- --b_c <= (datax(7)and(not datay(7))) or equ(0) or equ(1) or equ(2) or equ(3) or equ(4) or equ(5) or equ(6) or equ(7);

-

-

- b_c <= (datax(7)and(not datay(7))) or

- (buff_e(7) and (datax(6) and(not datay(6)))) or

- (buff_e(7) and buff_e(6) and (datax(5) and(not datay(5)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and (datax(4) and(not datay(4)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and (datax(3) and(not datay(3)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and (datax(2) and(not datay(2)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and (datax(1)and(not datay(1)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and buff_e(1) and (datax(0)and(not datay(0)))) or

- (buff_e(7) and buff_e(6) and buff_e(5) and buff_e(4) and buff_e(3) and buff_e(2) and buff_e(1) and buff_e(0) and c_in);

- END behavior;

但是,生成的RTL电路结构并非我想要的形式,实际生成的RTL电路采用了多级级联的与方式,这样导致了仿真出现很多毛刺,RTL 电路如下图:

我的想法是这些逻辑与门应该是多输入的方式存在,而非级联,就算浪费点,速度也不会太慢。

想请教大家的是,我该如何做呢?或是如何设置呢?

一周热门 更多>