- /////////////////sdi数据输出控制//////////////////////////////

- always [url=home.php?mod=space&uid=72445]@[/url] (negedge clk_ad or negedge cnv_reg or negedge rst_n ) //由于ADC是在SCK时钟的上升沿锁存数据,所以需要在SCK的下降沿将数据输出,以满足一定的建立时间

- begin //而且第一个SDI上的数据是由CNV的下降沿触发

- if(!rst_n)

- sdi_reg<=1'b1; //如果复位,则使SDI输出为高

- else

- if(wr_done)

- begin

- if(sdi_en)

- sdi_reg<=1'b0;

- else

- sdi_reg<=1'b1;

- end

-

- else

- begin

- if(sdi_en)

- sdi_reg<=cmd[Data_length-cnt1];

- else

- sdi_reg<=1'b1;

-

- end

- end

- /////////////////////////////////////////////////////////////

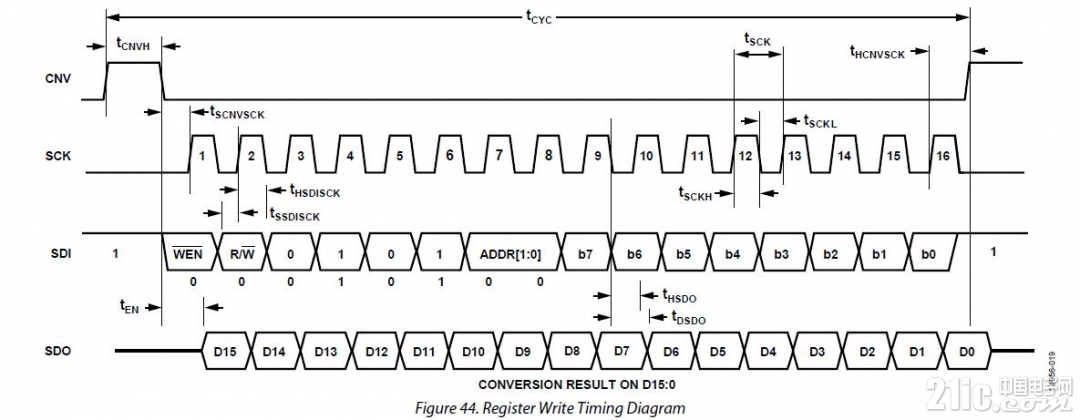

clk_ad是向ADC输出的时钟即SCK,cmd是要写的指令,用于设定ADC为TURBO模式,wr_done是写数据是否完成的标志。向ADC写数据的时序如下图所示

编译之后总是显示 if(wr_done) 这一行有错误,

错误为:

Error (10200): Verilog HDL Conditional Statement error at AD4000_Interface.v(305): cannot match operand(s) in the condition to the corresponding edges in the enclosing event control of the always construct

求大神指点

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>