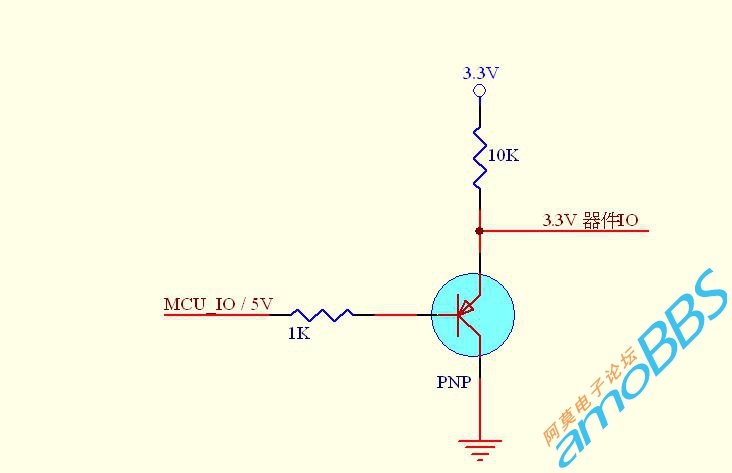

如圖,MCU為5V的單片機,現需要控制一個3.3V供電的一個IO,請問這個電路是否可靠,5V會從B极串到3.3V器件上嗎?

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

未命名.JPG (54.1 KB, 下载次数: 0)

下载附件

2012-9-18 17:23 上传

实测正如你所说,PNP导通时为0.7V,高电位为3.3V,有一点没有明白,请指教,B极低电位时,PNP导通,3.3V器件的IO应该是被拉低到地,怎会不是0V而是0.7V? 另外如何才能将IO拉到更低的电位,用PMOS会更好吗?

要想拉到更低的电位,可把那个PNP型的三极管接成共发射极方式(即把10K电阻移到下方),再加一只NPN型三极管用以反相即可(当然,加上的三极管B极要加限流电阻、C极与3.3v之间要有上拉电阻,这样算来实际上要加三个元件了)。这种方式的好处是:不管是哪边的电压高低都适用,而且两边电压相差很大(比如相差十几伏)也无妨。

简单点的,MCU开漏输出加3.3V上拉,然后直连3.3V器件IO。

或者两只电阻分压后连接即可。

以上只针对你给出的图纸,如果两端还有其它电路相连,则还需要考虑各电路间的配合问题。

直接改用PMOS的话,情况会更糟,那时就不是0.7V ,而应该是1.5V以上了。

一周热门 更多>