例说FPGA连载45:DDR控制器集成与读写测试之板级调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

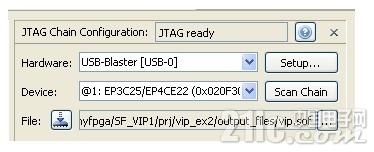

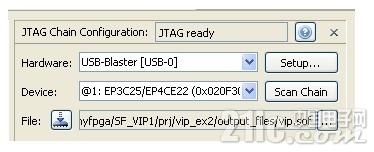

① 打开“…prjvip_ex2”文件夹下的工程。② 点击Quartus II菜单栏的“ToolsàIn-System Memory Content Editor”,在界面的右侧,如图4.25所示,选择“…prjvip_ex2output_files”文件夹下的vip.sof,执行下载操作,即点击File右侧的小按钮。

图4.25 JTAG下载配置界面③ 下载完成后可以看到VIP板上的指示灯D1闪烁。此时我们接着选中Index下面的Memory项,然后单击循环读取按钮,如图4.26所示。

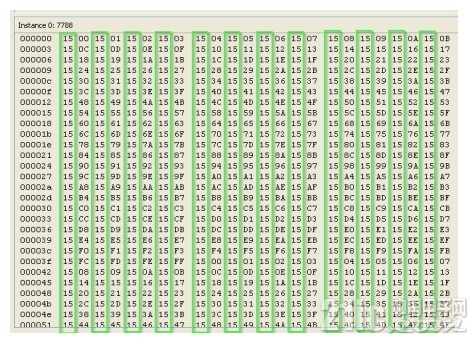

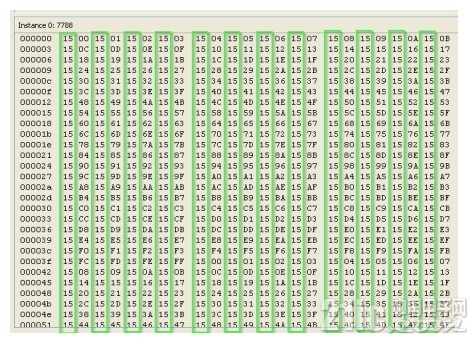

图4.26 可在线查看的片内RAM④ 接着我们可以观察Memory当前的数据变化。如图4.27所示,矩形框起来的高字节数据,即我们每隔一秒多统一递增一次的数据,而其后的低字节数据则始终是从0开始递增和地址一一对应的递增数据。因此,我们看到的实验结果是,这个onchip RAM的所有16bit的高字节每隔一秒都会递增一,而其后的数据则一直保持当前状态不变。

图4.27 递增的DDR2读出数据

一周热门 更多>