例说FPGA连载42:DDR控制器集成与读写测试之DDR2 IP核接口时序特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

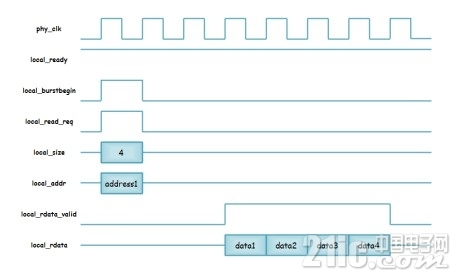

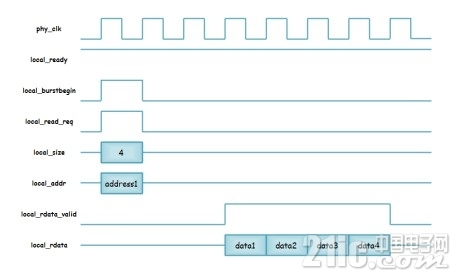

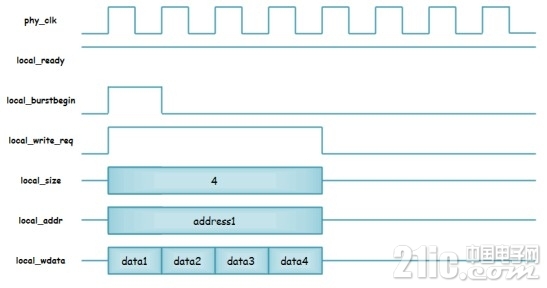

用户逻辑和DDR2 IP核之间的接口并不是什么新发明的特殊接口,不过是Avalon-MM总线而已。有人说这个美眉(Memory-Map)会不会太慢了,关键时刻耽误事?非也,MM总线的burst模式也可以流水线式连续传输数据,丝毫不逊 {MOD}于ST(stream)传输方式。 这里我们可以简单了解一下带“local_*”的Avalon-MM总线burst模式传输协议的使用方法。 可以比较简单山寨的理解前面已经给出的带“local_*”的Avalon-MM信号接口:● local_size为burst读写的最大数据数量。通常IP核内部有FIFO用于支持这样的连续数据读写,在Megafunction中设定好的最大数据数量是Avl_size的上限值。● local_be为byte enable信号,用于使能或说是屏蔽读写数据的各个高低字节。● local_ready为总线当前状态指示。这里高电平表示ready,此时的local_read_req和local_write_req能够被锁存。● local_burstbegin为突发传输起始标志位。它不受local_ready的影响,在发起一次读或写操作的第一个时钟周期,只需保持一个时钟周期的local_burstbegin为高电平状态,并且不用管此时的local_ready状态如何。● local_addr为读写共用的总线地址,位宽由DDR2的存储总量和总线上读写数据的位宽来决定。如1Gbit的DDR2,外部芯片的数据位宽为16bit,Avalon-MM读写的数据位宽64bit,那么它的地址不是以16bit位宽来计算的,而是以64bit位宽来计算的,即16M(24位)。● local_read_req为读请求,配合地址local_addr和突发传输起始标志位local_burstbegin发起一次burst读操作。在local_burstbegin拉高后,只需要确保在同一个时钟周期或其后第一次local_ready有效的时钟周期拉高一次local_read_req信号即可。● local_rdata_valid为读出数据的有效标志位。IP核在收到burst读请求(local_read_req)后的若干个时钟周期开始连续送出数据(数据可能分多次连续送出),该信号和读出数据配合,高电平表示当前读出数据有效。● local_rdata为读出数据。和local_rdata_valid配合送给用户逻辑。● local_write_req为写请求信号。若发起一次n个数据写入的burst传输,第一个传输时钟周期首先拉高local_burstbegin以及local_write_req,且local_write_req必须保持到n个数据写入完成。只有在local_ready有效时,当前的local_write_req、local_addr和local_wdata才是有效的。● local_wdata为写入数据。 接着我们再用几张时序图来解析前面的接口。① 如图4.14所示,正常4个数据的burst读操作。默认情况下,local_addr为读出的首个数据对应的地址,随后将读出递增地址的数据。

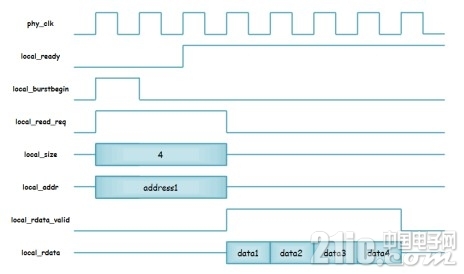

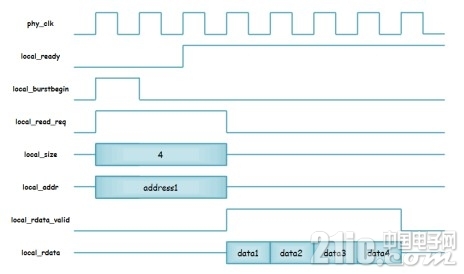

图4.14 四个数据读取操作时序② 如图4.15所示,遇到local_ready拉低的读操作,必须保持local_read_req、local_size和local_addr到local_ready拉高为止。

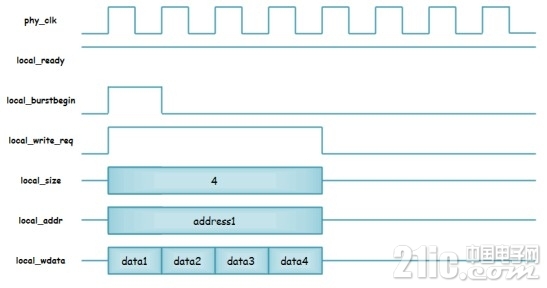

图4.15 读忙时的四个数据读取时序③ 如图4.16所示,正常4个数据的burst写操作。默认情况下,local_addr设定的是写入的首个数据对应的地址,随后每次写入数据后地址自动递增。

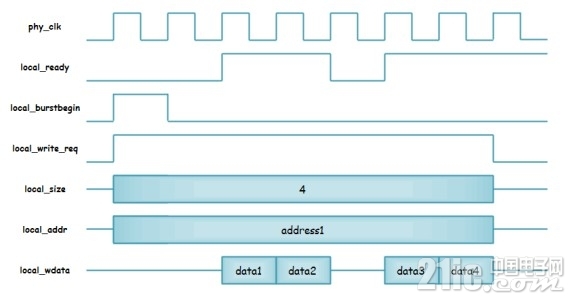

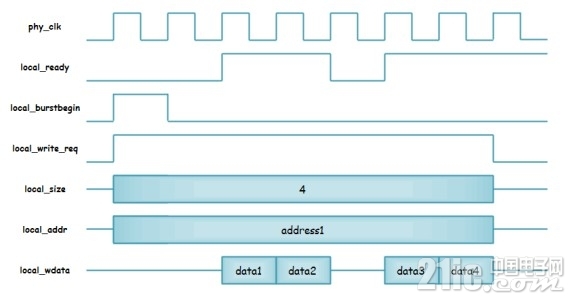

图4.16 四个数据写取操作时序④ 如图4.17所示,遇到local_ready拉低的4个数据的burst写操作。Local_ready拉高时,local_write_req、local_addr和local_wdata所对应的地址和数据才是有效的。

图4.17 写忙时的四个数据写时序

一周热门 更多>