例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

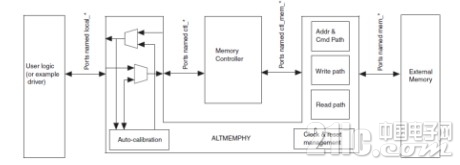

如图4.13所示,这是DDR2 IP核与外部接口的功能框图。

图4.13 DDR IP核功能框图● 图左侧为用户逻辑(User logic),它与DDR2 IP核的接口通常命名为“local_*”;图右侧为FPGA外部的DDR2芯片,它与DDR2 IP核的接口通常命名为“mem_*”。● DDR2 IP核内部分两个部分,即图示的“ALTMEMPHY”和“存储控制器(Memory Controller)”,正如图中所示,它们各有分工。存储控制器产生DDR2芯片实际读写操作需要的时序;ALTMEMPHY有两部分功能,一个功能是对DDR2做自动校正(Aoto-Calibration),另一个功能是实现DDR2所需的物理接口。● DDR2的自动校正是在初始化阶段进行的,此时ALTMEMPHY断开用户逻辑和存储控制器之间的接口,ALTMEMPHY产生存储控制器所需的DDR2读写控制,直到校正完成。在初始化过后,ALTMEMPHY将不再需要控制存储控制器,而是一直保持用户逻辑和存储控制器的连通。● 另外,图中未明确示意,实际上这个DDR2 IP核还包括了一个PLL,用于时钟的管理。 现在我们来看ddr2_controller模块例化的接口。这里可以分为三大类,第一类为系统类接口,主要是一些系统或PLL的复位、时钟等接口;第二类为带“local_*”的接口,是DDR2 IP核与用户逻辑间的接口;第三类为带“mem_*”的接口,是DDR2 IP核与FPGA外部DDR2芯片的接口。 对于第一类接口,功能描述如表4.1所示。表4.1 DDR2 IP核系统接口列表信号名方向功能描述global_reset_nInputIP核的全局异步复位信号,低电平有效。该信号有效时,将使得ALTMEMPHY(包括PLL)都进入复位状态。pll_ref_clkInputPLL的输入参考时钟信号。soft_reset_nInputIP核的全局异步复位信号,低电平有效。该信号只能复位ALTMEMPHY,而不能复位PLL。aux_half_rate_clkOutputphy_clk时钟信号的引出,时钟频率与phy_clk一样,可用于用户逻辑使用。aux_full_rate_clkOutputphy_clk时钟信号的引出,时钟频率是phy_clk的两倍,可用于用户逻辑使用。reset_request_nOutput复位输出,用于指示用户逻辑DDR2 IP核的内部PLL输出locked还未完成。phy_clkOutputALTMEMPHY产生供用户逻辑使用的半速率时钟信号。所有输入和输出到ALTMEMPHY的用户逻辑接口信号,都与此时钟同步。reset_phy_clk_nOutput与phy_clock时钟域相关的复位信号,低电平有效。可用此时钟复位所有DDR IP核和用户逻辑接口相关的信号。

一周热门 更多>