例说FPGA连载38:DDR控制器集成与读写测试之FPGA片内RAM概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

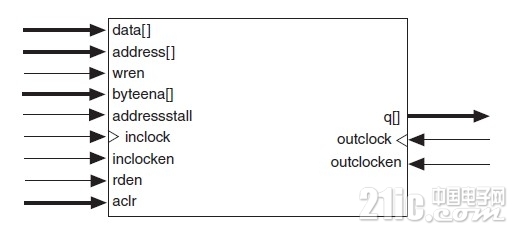

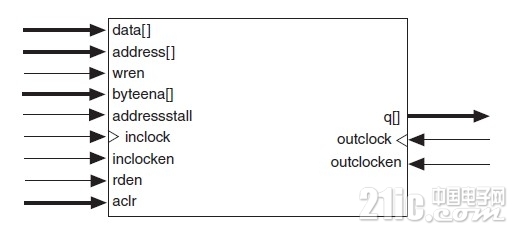

我们所使用的Cyclone IV系列FPGA器件内嵌丰富的M9K存储器,M9K存储器支持以下特性。● 每个M9K存储块有8192 bits的存储量。● 每个端口拥有独立的读使能和写使能信号。● 可变的端口配置。● 所有位宽都支持单端口或者双端口模式。● 每个端口都有可选的时钟使能信号。● RAM或ROM模式下可以初始化预加载存储数据。本实例我们要用Cyclone IV的片内存储器配置一个RAM。如图4.2所示,这是单端口RAM模式下的接口示意图。当然了,并非这里所罗列的所有接口都一定要用到,除了一般性的写入数据总线data[]、地址总线address[]、写使能信号wren、写时钟inclock(可以和outclock共用同一个时钟)、读出数据总线q[]这几个接口外,其他接口都是可选接口,可以根据用户实际应用需求添加或删除。

图4.2 RAM接口示意图

一周热门 更多>