使用FPGA时钟展频技术搞定RE测试特权同学原创,转载请注明出处1 关于时钟展频应用展频技术是通过对尖峰时钟进行调制处理,使其从一个窄带时钟变成为一个具有边带谐波的频谱,从而达到将尖峰能量分散到展频区域的多个频率段,达到降低尖峰能量,抑制EMI的效果。

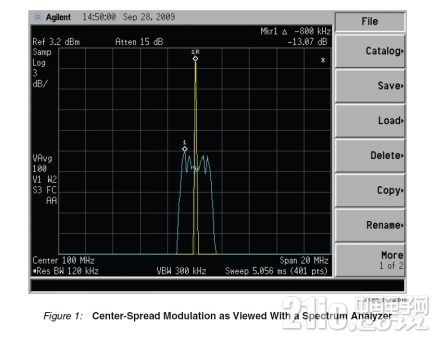

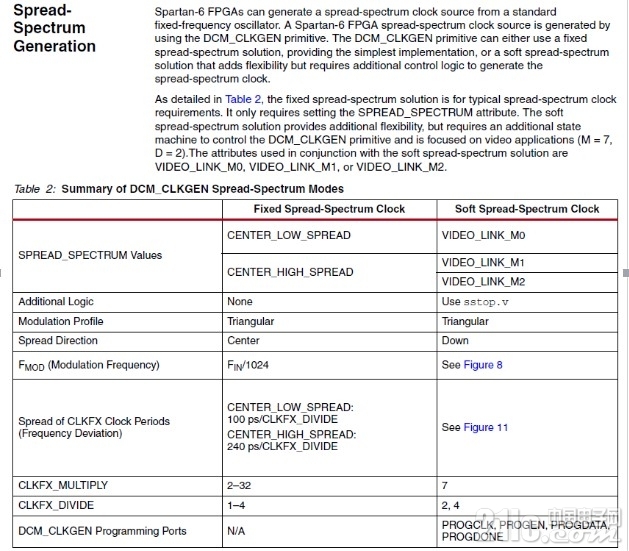

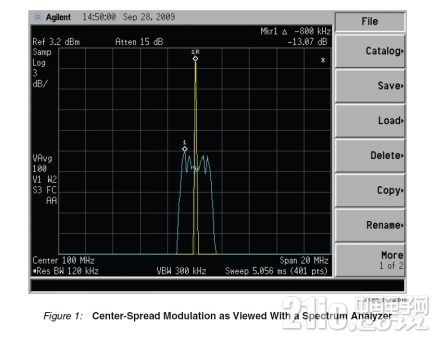

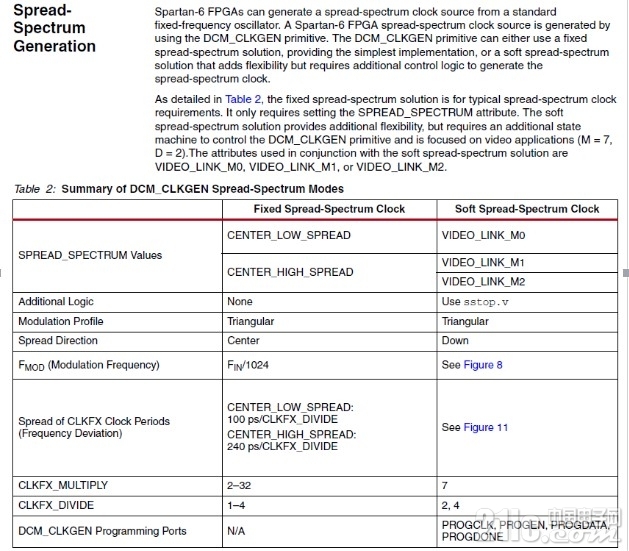

2 Altera FPGA的时钟展频支持 Altera的PLL IP核带有展频功能。当然,这种展频功能块应该是“硬核”实现,在某些特定器件上才能够支持。file:///C:UserspcAppDataLocalTempksohtmlwpsB29D.tmp.jpg 参考:http://www.topleve.com/upfile/2015122510365534.pdf 3 Xilinx FPGA的时钟展频支持 Xilinx FPGA也有很好的时钟展频支持,以低端应用的Spartan6为例,官方文档xapp1065.pdf中有如下描述。

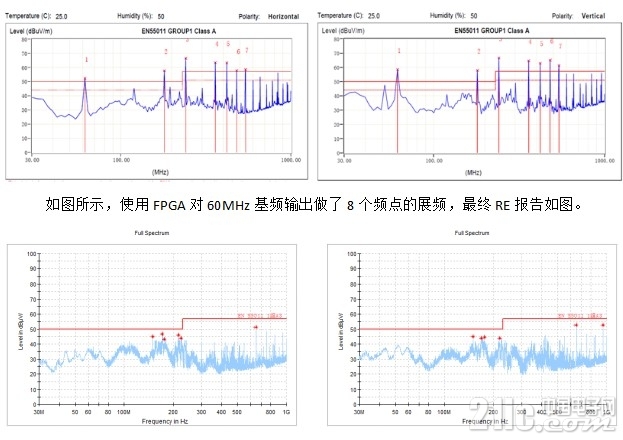

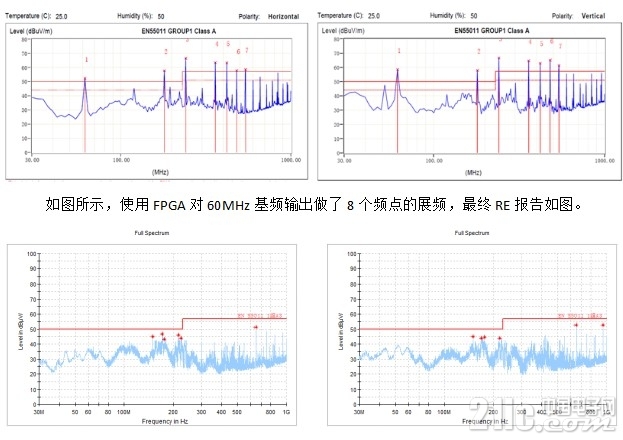

4 FPGA的时钟展频案例 特权同学在实践中尝试了一把,非常奏效。某Class A标准的产品在初测RE时,报告如下,明显很多60MHz基频的辐射点超出很多。辐射点的能量很集中的一个点上。

如图所示,使用FPGA对60MHz基频输出做了8个频点的展频,最终RE报告如图。

一周热门 更多>