例说FPGA连载36:DDR控制器集成与读写测试之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

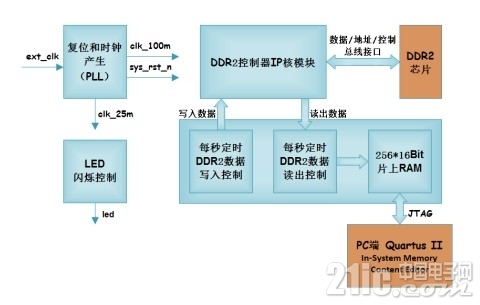

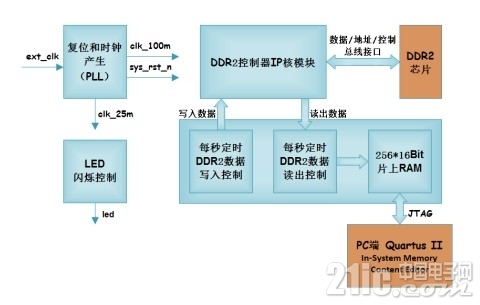

本实例对Altera提供的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次DDR2的写入和读出操作。先是从0地址开始遍历写256*64bits数据到DDR2的地址0-1023中;在执行完写入后,执行一次相同地址的读操作,将读出的256*64bits数据写入到FPGA的片内RAM中。在Quartus II集成的In-System Memory Content Editor中可以查看片内RAM中规律变化的数据。本实例系统功能框图如图4.1所示。

图4.1 工程实例2功能框图

一周热门 更多>