1 凑到512,写数据的一方把剩下的写0,凑够512个。但这个效率不高,不想用。

2 利用FIFO的WRUSEDW和RDUSEDW两个数据,在FPGA中调整FULL和EMPTY信号。(其实不是FIFO自动的FULL和EMPTY,但代表我要写的数据已经够了或者空了)

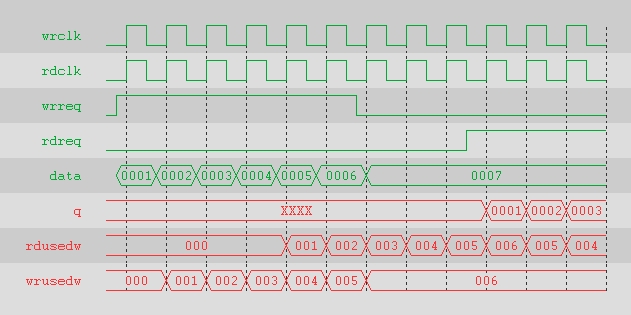

现在的问题是:我一向理解这两个数据是代表FIFO中的实际个数,两者应该一致,只不过是所依据的反转沿不同,但QUARTUS提供的仿真时序却不是如此,见下图:数据被读之后WRSUEDW并没有发生变化。除非该信号有延迟,图片显不出来,但会延迟这么多吗?

不知道有没有用过类似的应用的大虾,对深度不是2的整数次幂,会如何做?

谢谢。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

既然2这应该一致,怎么要弄2个呢。

我的也是altera 生成的。或者我们操作不一致。

我不明白你的方案。空就写,另一方,有数就读,这应该是fifo 的基本功能。没必要凑数

一周热门 更多>