本帖最后由 pjzmj2012 于 2016-8-16 15:23 编辑

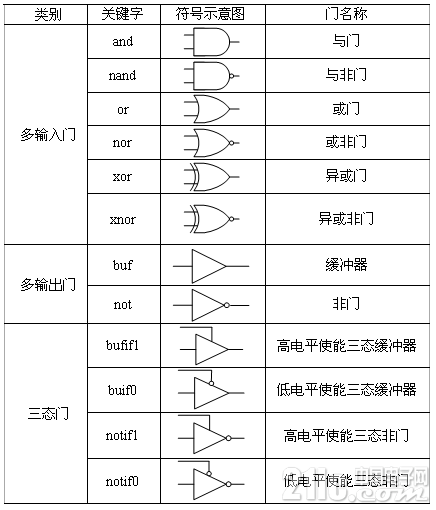

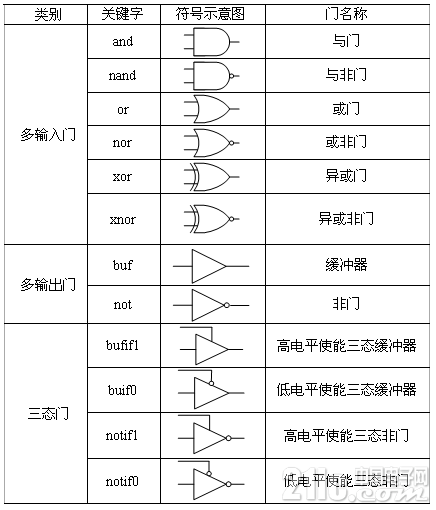

其中,普通门的端口列表

门元件名字<例化的门名字>(输出,输入1,输入2,输入3...);如:

and a1(out,int1,int2,in3);//三输入与门

而对于三态门

bufif1 mytri1(out,in,enable);//高电平使能的三态门

(输出,输入,时能控制端)

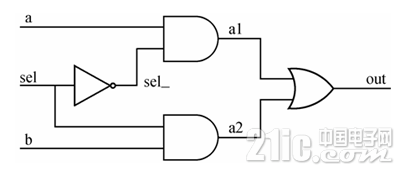

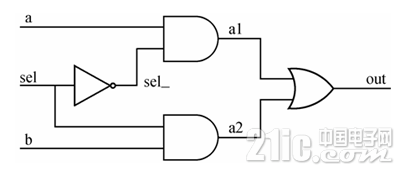

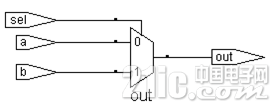

例1:门级结构的二选一MUX

module MUX1(out, a, b, sel);output out;input a, b, sel;not (sel_, sel);and (a1, a, sel_), (a2, b, sel);or (out, a1, a2);endmodule

例2:行为描述2选1MUXmodule mux2(out, a, b, sel);output out;input a, b, sel;reg out;always @(a or b or sel)begin if(sel) out = b; else out = a;endendmodule

例3:数据流描述的2选1MUXmodule MUX3(out, a, b, sel);output out;input a, b, sel;assign out = sel? b : a;endmodule

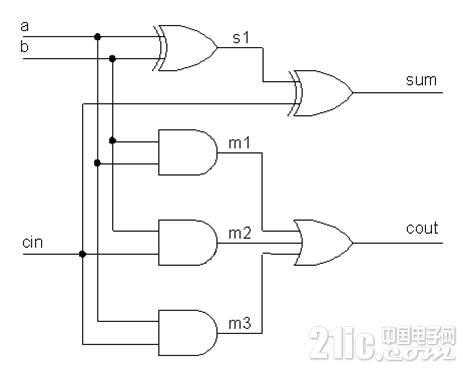

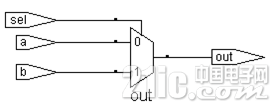

例4:结构描述的1位全加器

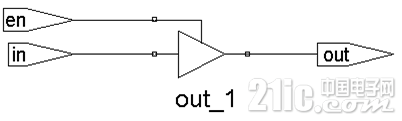

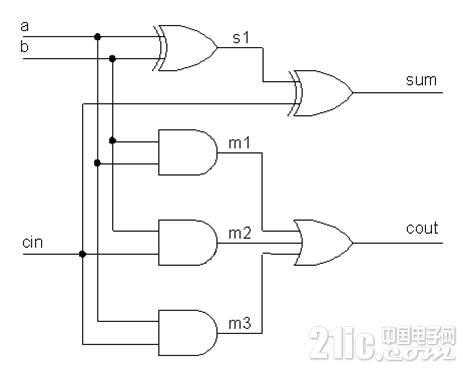

module full_add1(a, b, cin, sum, cout);input a, b, cin;output sum, cout;wire s1,m1, m2, m3;and (m1, a, b), (m2, b, cin), (m3, a, cin);xor (s1, a, b), (sum, s1, cin);or (cout, m1, m2, m3);endmodule例5:数据流描述的1位全加器module full_add2(a, b, cin, sum, cout);input a, b, cin;output sum, cout;assign sum = a ^ b ^ cin;assign cout = (a & b ) | (b & cin) | (cin & a );endmodule例6:行为描述的1位全加器module full_add4(a,b,cin,sum,cout);input a,b,cin; output sum,cout;reg sum,cout,m1,m2,m3;always @(a or b or cin)begin m1=a&b; m2=b&cin; m3=a&cin;sum=(a^b)^cin;cout=(m1|m2)|m3;endendmodule例7:用bufif1关键字描述的三态门

module tri_1 (in, en, out);input in, en;output out;tri out;bufif1 b1(out, in, en);endmodule 例8:3—to—8 decoder

module decoder_38(out, in);output[7:0] out;input[2:0] in; reg[7:0] out;always @(in) begin case(in) 3'd0: out=8'b11111110; 3'd1: out=8'b11111101; 3'd2: out=8'b11111011; 3'd3: out=8'b11110111; 3'd4: out=8'b11101111; 3'd5: out=8'b11011111; 3'd6: out=8'b10111111; 3'd7: out=8'b01111111; endcase endendmodule

其中,普通门的端口列表

门元件名字<例化的门名字>(输出,输入1,输入2,输入3...);如:

and a1(out,int1,int2,in3);//三输入与门

而对于三态门

bufif1 mytri1(out,in,enable);//高电平使能的三态门

(输出,输入,时能控制端)

例1:门级结构的二选一MUX

module MUX1(out, a, b, sel);output out;input a, b, sel;not (sel_, sel);and (a1, a, sel_), (a2, b, sel);or (out, a1, a2);endmodule

module decoder_38(out, in);output[7:0] out;input[2:0] in; reg[7:0] out;always @(in) begin case(in) 3'd0: out=8'b11111110; 3'd1: out=8'b11111101; 3'd2: out=8'b11111011; 3'd3: out=8'b11110111; 3'd4: out=8'b11101111; 3'd5: out=8'b11011111; 3'd6: out=8'b10111111; 3'd7: out=8'b01111111; endcase endendmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

LZ头像好面熟。

哈哈 我是小号

一周热门 更多>