例说FPGA连载17:时钟与复位电路设计特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

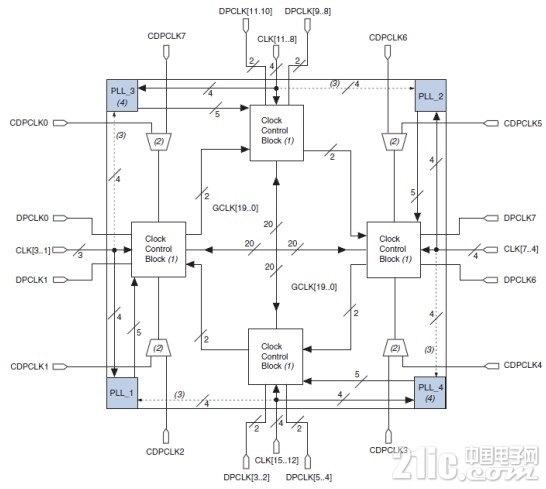

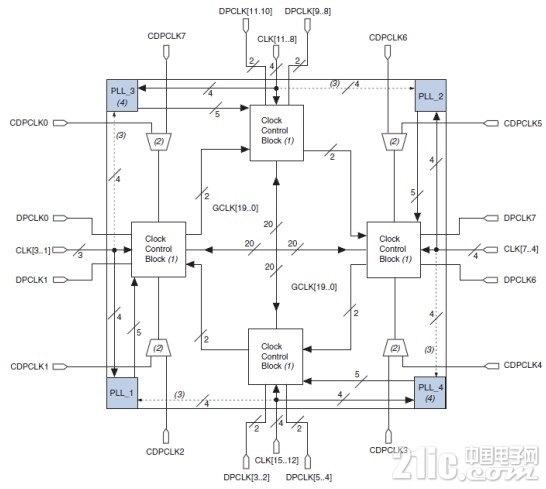

FPGA的时钟输入都有专用引脚,通过这些专用引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位通常是需要走全局时钟网络的。如图2.15所示,这是Cyclone IV器件的内部全局时钟网络的布局示意图。如果说一个城市当中的各种羊肠小道、普通马路是FPGA器件内部的一般布线资源,那么我们就可以认为FPGA内部的全局时钟网络就是高架路(高速公路)。图中我们也不难发现,除了FPGA外部的一些专用时钟引脚,PLL的输出以及FPGA内部的一些信号也都可以连接到FPGA的全局布线网络上。

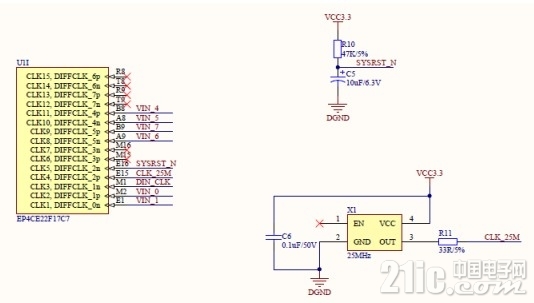

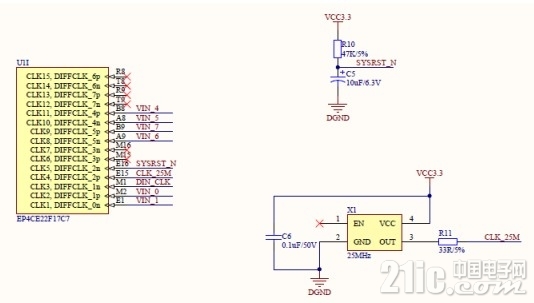

图2.15 FPGA全局时钟网络时钟和复位电路如图2.16所示。外部使用了25MHz的有源晶振,连接FPGA的专用时钟输入引脚,FPGA内部的PLL可以将外部时钟频率进行倍频或分频,甚至进行相位的调整。复位使用简单的RC电路,也是连接到FPGA的专用输入时钟引脚,走内部全局时钟网络。

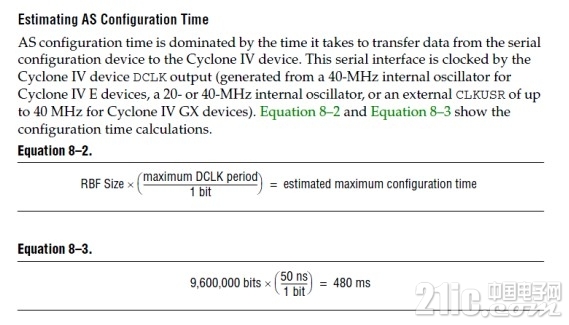

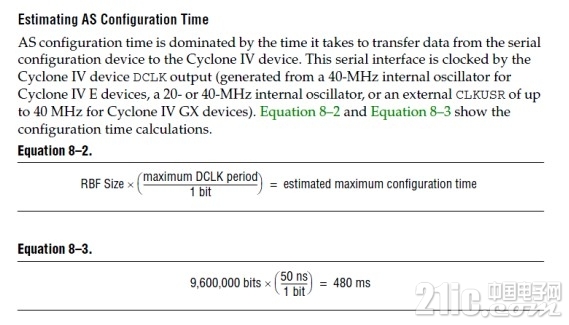

图2.16 FPGA时钟和复位电路FPGA上电复位时间需要大于FPGA器件启动后的配置加载时间,这样才能够确保FPGA运行后的复位初始化过程有效。因此,我们也可以来看看这个电路的设计是否满足实际要求。如图2.17所示,这是器件手册中关于上电配置时间的计算公式。

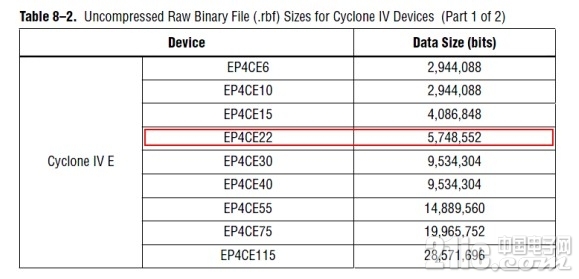

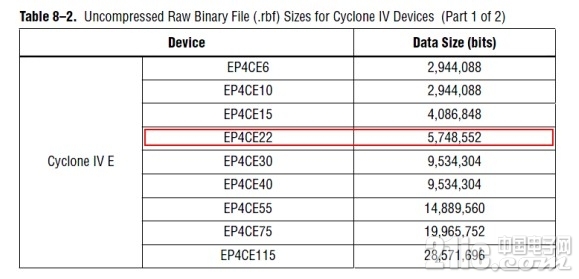

图2.17 器件手册中AS配置时间计算公式的截图如图2.18所示,我们所使用的EP4CE22器件的配置数据量为5,748,552bits。

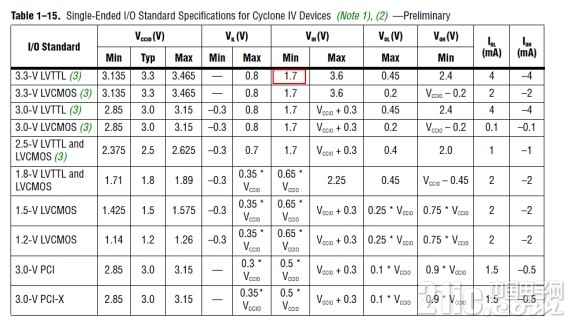

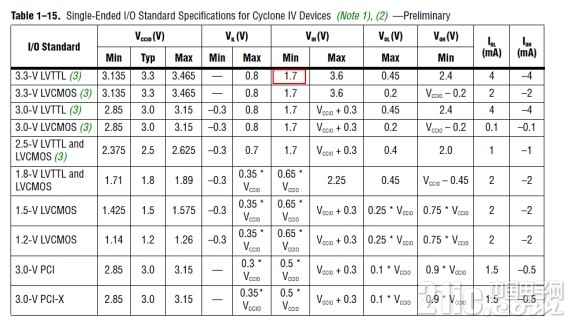

图2.18 器件手册中配置数据存储量的截图我们实测当SPI Flash对FPGA进行配置时的时钟为32MHz。由此我们便可以计算配置所需的时间,取最坏的情况,即配置时钟频率在最低情况下,配置所需时间为:5748552bits*(31.25ns/1bit) = 180ms。如图2.19所示,这里标示了复位输入引脚作为3.3-V LVTTL标准电平的最低VIH电压值是1.7V,那么可以由此计算阻容复位电路从0V上升到1.7V所需的时间。

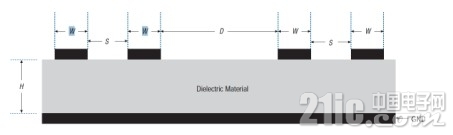

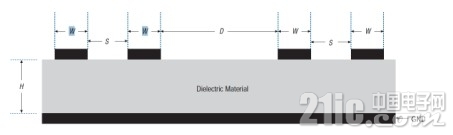

图2.19 器件手册中I/O电平标准的截图设V0 为电容上的初始电压值;V1 为电容最终可充到或放到的电压值;Vt 为t时刻电容上的电压值。则有公式t = RC*Ln[(V1-V0)/(V1-Vt)]。求充电到1.7V的时间。将已知条件V0=0,V1=3.3V,Vt=1.7V代入上式得: 1.7=0+3.3*[[1-exp(-t/RC)],算得t = 0.7239RC。代入R=47k ,C=10uf得t = 0.34s,即340ms。由此我们验证了阻容复位的时间远大于FPGA器件的上电复位时间。当然了,这里没有考虑FPGA器件从上电到开始配置运行所需的电压上升时间,一般这个时间不会太长。所以我们的阻容复位肯定是有效的。如果需要实际的确认,还是要通过示波器设备来辅助观察实际信号的延时情况。关于FPGA时钟电路的PCB Layout设计,通常需要遵循以下的原则。● 时钟晶振源应该尽可能放在与其连接的FPGA时钟专用引脚的临近位置。● 时钟线尽可能走直线。如果无法避免转弯走线,使用45度线,尽量避免T型走线和直角走线。● 不用同时在多个信号层走时钟线。● 时钟走线不要使用过孔,因为过孔会导致阻抗变化及反射。● 靠近外层的地层能够最小化噪声。如果使用内层走时钟线,要有良好的参考平面,且走带状线。● 时钟信号应该有终端匹配电路,以最小化反射。● 尽可能使用点到点的时钟走线。● 如图所示,对于时钟差分对的走线,必须严格按照D>2S规则,以最小化相邻差分对间的串扰。

图2.20 时钟差分对的间隔● 确保整个差分对在整个走线过程中的线间距恒定。● 确保差分对的走线等长,以最小化偏斜和相移。● 同一网络走线过程中避免使用多个过孔,以确保阻抗匹配和更低的感抗。● 高频的时钟和USB差分信号对走线尽可能短。● 高频时钟或周期性信号尽可能远离高速差分对以及任何引出的连接器(例如I/O连接器、控制和数据连接器或电源连接器)。● 应当保证所有走线有持续的地和电源参考平面。● 为了最小化串扰,尽量缩短高频时钟或周期性信号与高速信号并行走线的长度。推荐的最小间距是3倍的时钟信号与最近参考面间距。● 当一个时钟驱动多个负载时,使用低阻抗传输线以确保信号通过传输线。● 信号换层时使用回路过孔。● 同步时钟的延时应该与数据相匹配。确保时钟与同步数据总线在同一层走线,以最小化不同层之间的传输速率差异。

一周热门 更多>