大家好, 小弟想用FPGA的专用LVPECL端口接收来自高速比较器的LVPECL信号,比较器输出的信号是连续两个1ns的高电平脉冲,脉冲间距是0.6ns,不知道这样的信号能否通过FPGA的LVPECL端口灌到FPGA内部呢?我用的器件是SPARTAN 3E xc3s250

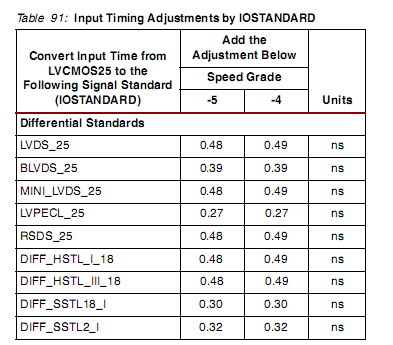

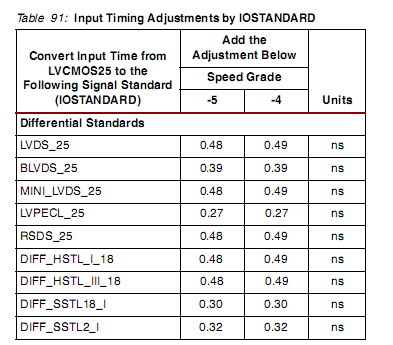

datasheet中有这样一个表格,看到LVPECL_25到LVCMOS25 的转化时间最短到0.27ns,是不是说我这个0.6ns的信号脉宽,还是有可能灌到内部逻辑的?

要是真的可以就好了。。。

多谢啦~

datasheet中有这样一个表格,看到LVPECL_25到LVCMOS25 的转化时间最短到0.27ns,是不是说我这个0.6ns的信号脉宽,还是有可能灌到内部逻辑的?

要是真的可以就好了。。。

多谢啦~

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

谢谢谢谢~幸好还没有发板,否则就浪费了。。

去看一下TDC-GP2这个芯片

一周热门 更多>