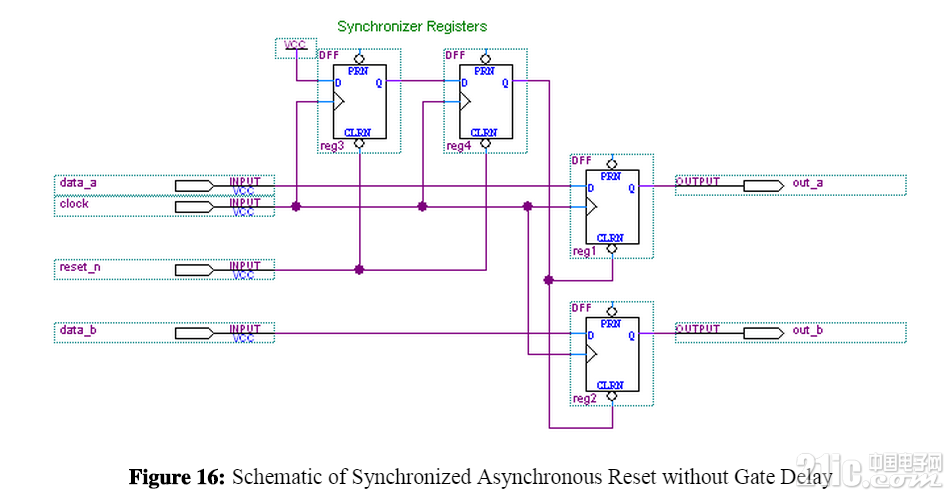

altera官方给出的设计,现有以下疑问,请高手帮忙分析下:

目的将电路设计成异步复位,但复位信号释放时与CLK同步,目的在复位信号释放时变得与CLK边沿同步,便于分析问题(个人看来无法降低亚稳态发生概率)。如下图中reg4,在reset_n生效时,可同时输出复位reg1,reg2,但同样,reset_n释放可能发生在clk生效时(造成触发器无法判断resetn状态),造成亚稳态,在我看来reg1,reg2发生亚稳态概率一样,因为概率都是受到resetn频率及clk频率影响,而reg4发生亚稳态后,输出状态必定影响到reg1.2的状态,因此多级D触发器于事无补(针对复位情况,如果是数据D经过多级触发器输入当然有作用)。

另外,有一种说法就是复位发生后,reg4原来输入端为0,因此无论clr端为0或者1,reg4输出均为0,但实际上亚稳态发生与输入D并无关系,输出可能是震荡、毛刺,因此这种说法应该不正确啊。

求解答。如实实现同步释放的,即怎么实现在clk边沿有效时,才判断resetn信号是否有效,个人认为只要接了触发器clr端,就没法实现同步释放了,因clr复位根本不受clk控制。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

首先非常感谢回复。

我是个新手,再追问下,按您说的,复位释放同步,即释放相位一致,2级D触发器确实做到了同步退出,相对于异步复位,这个是有区别的,这个我能理解。但单看reg4,可以看成这就完全是一个异步复位电路,因此clr和reset如果不满足一定关系还是一样会引起亚稳态,我想弄清楚的是,假如在clk上升沿到来时reg4无法判断clr端状态,这时候如果reg4输入D端有稳定的数据0,其输出到底是稳定的0,或是由于reg4无法判断clr状态,而导致输出震荡,或是导致触发器不断复位,如果是不断复位确实没有问题,但是如果是输出震荡或者毛刺还是会对后级触发器产生影响的吧,毕竟reg4输出是作为其他触发器的复位信号的,震荡的信号可能被其他触发器错误识别,导致不断复位?

首先,复位问题之所以采用同步释放,是因为复位生效后,就算发生亚稳态,也已经可以不关注了,因为后级寄存器都已经复位了,就算输入是亚稳态有什么关系? 所以你提到的“reg4发生亚稳态后,输出状态必定影响到reg1.2的状态”,站不住脚。

复位采用“异步复位,同步释放”,主要是解决复位释放时,正好撞在时钟沿附近所产生的问题。reg3,和reg4组成的“Synchronizer Registers”的作用你没有仔细分析。你仔细看好了:

复位释放时,就算这时正好在时钟沿附近,但是这时reg3也还没有完全退出复位状态,所以reg4的输入端就是“稳定”的低电平,因此reg4就会输出稳定的低电平,不会有亚稳态;

然后等到第二个时钟沿,这时reg3,、reg4都已经退出复位状态了,reg3的输出是稳定的高电平,但是这个周期reg4还是输出低,因为它的输入还是低电平,reg3输入的高电平还无法反应到reg4的输出端来。

等到第三个周期的时候,reg4才稳定的输出高电平。

并且这个从低到高的转换是每次复位释放后都确定的发生在时钟沿之后一点(寄存器Tco的延迟),这样这个信号布线到系统内部的各个寄存器的时候,就有将近一个时钟周期的布线延迟,从而可以保证系统内的每个寄存器的复位释放都是在同一个时钟沿处生效。

如果不是这种方式,复位从低到高于时钟的相位是随机的,那么在有些复位释放情况下,就会发生系统内一些寄存器在前一个时钟沿退出复位,另外一些寄存器在下一个时钟沿才退出复位的情况。也就是大家不同步。

楼主把这个10多年前的文档仔细看完就明白了。

----- 反过来想,如果真有问题,10多年了,早就有人给他提出来了。呵呵

一周热门 更多>