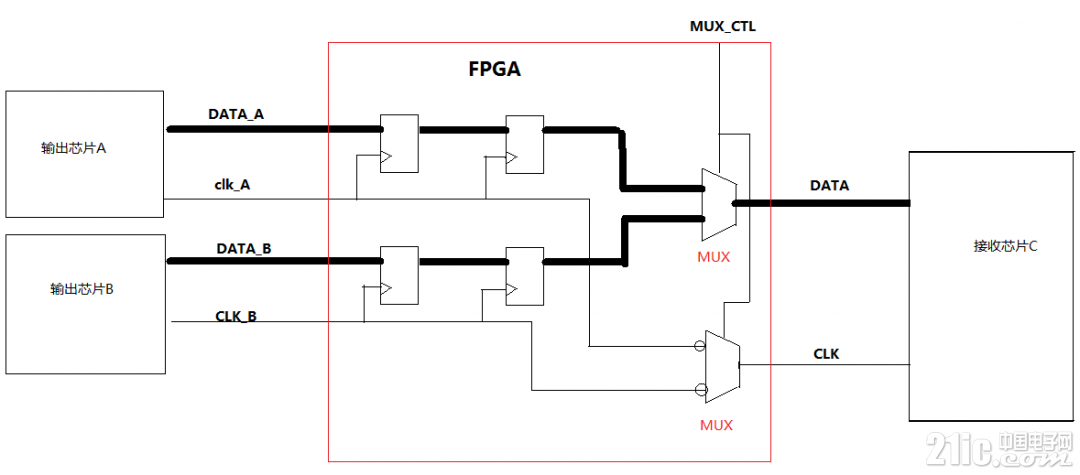

这个项目是原来做过的,用的cyclone2去做的,quartus7的开发工具,

quartus老版本的约束是基于它自己的qsf约束命令。

后来产品小升级,芯片也换成了cyclone4去,只能用quartus12去搞,

新版的工具也改为sdc约束,做出产品后,发现后端芯片采集的不正确,仔细分析后,

可以确认是数据错位,也就是fpga的建立保持时间约束不对或是没达到要求。

研究了有一段时间了,还没完全搞明白,大侠帮指点下,看下我如下的约束,有没有问题

目标是需要跑到170M左右,实际只能跑到120M左右就开始出现采集的数据有问题了。

(原来cyclone2的平台上,可以稳定跑到195M以上),时钟约束是满足的,主要是建立保持时间的约束感觉不正确

和自己的理解有出入。。。

create_clock -name "clk_A" -period 5.800ns [get_ports {clk_A}]

create_clock -name "clk_B" -period 5.800ns [get_ports {clk_B}]

create_clock -name "clk" -period 5.800ns [get_ports {clk}]

set_input_delay -clock "clk_A" -max 3.8ns [get_ports {DATA_A}]

set_input_delay -clock "clk_A" -min 0.5ns [get_ports {DATA_A}]

set_input_delay -clock "clk_B" -max 3.8ns [get_ports {DATA_B}]

set_input_delay -clock "clk_B" -min 0.5ns [get_ports {DATA_B}]

set_output_delay -clock "clk" -max 2.5ns [get_ports {DATA}]

set_output_delay -clock "clk" -min -2ns [get_ports {DATA}]

set_max_delay 1.000ns -from [get_ports {*}] -to [get_ports {*}]

set_false_path -from "clk_A" -to "clk_B"

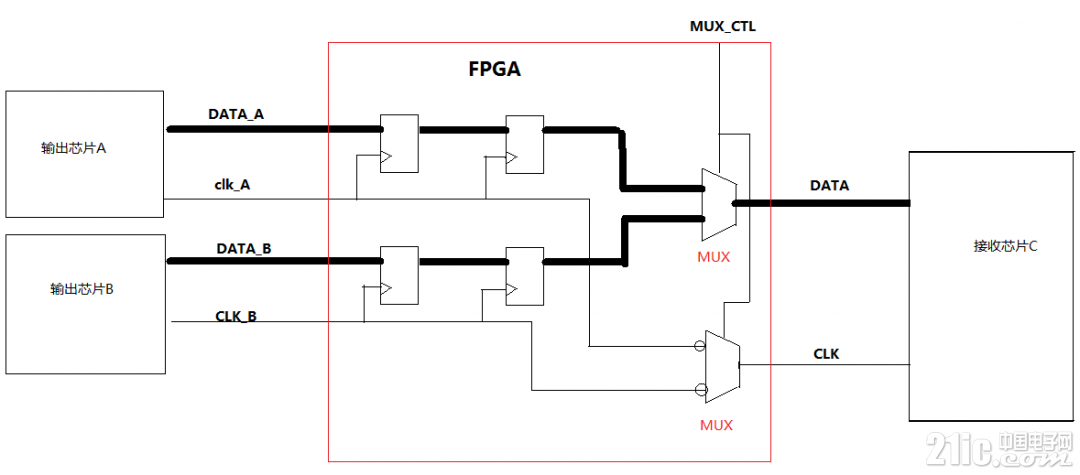

quartus老版本的约束是基于它自己的qsf约束命令。

后来产品小升级,芯片也换成了cyclone4去,只能用quartus12去搞,

新版的工具也改为sdc约束,做出产品后,发现后端芯片采集的不正确,仔细分析后,

可以确认是数据错位,也就是fpga的建立保持时间约束不对或是没达到要求。

研究了有一段时间了,还没完全搞明白,大侠帮指点下,看下我如下的约束,有没有问题

目标是需要跑到170M左右,实际只能跑到120M左右就开始出现采集的数据有问题了。

(原来cyclone2的平台上,可以稳定跑到195M以上),时钟约束是满足的,主要是建立保持时间的约束感觉不正确

和自己的理解有出入。。。

create_clock -name "clk_A" -period 5.800ns [get_ports {clk_A}]

create_clock -name "clk_B" -period 5.800ns [get_ports {clk_B}]

create_clock -name "clk" -period 5.800ns [get_ports {clk}]

set_input_delay -clock "clk_A" -max 3.8ns [get_ports {DATA_A}]

set_input_delay -clock "clk_A" -min 0.5ns [get_ports {DATA_A}]

set_input_delay -clock "clk_B" -max 3.8ns [get_ports {DATA_B}]

set_input_delay -clock "clk_B" -min 0.5ns [get_ports {DATA_B}]

set_output_delay -clock "clk" -max 2.5ns [get_ports {DATA}]

set_output_delay -clock "clk" -min -2ns [get_ports {DATA}]

set_max_delay 1.000ns -from [get_ports {*}] -to [get_ports {*}]

set_false_path -from "clk_A" -to "clk_B"

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

特意做了下后仿真,感觉sdc约束,搞的有点云里雾里。。。和自己理解的似乎出入很大。。。

Altera Xilinx 原装优势 QQ790498866

此外,你应该明白input delay和output delay中min和max分别指的是什么,这样才能正确约束。

一周热门 更多>