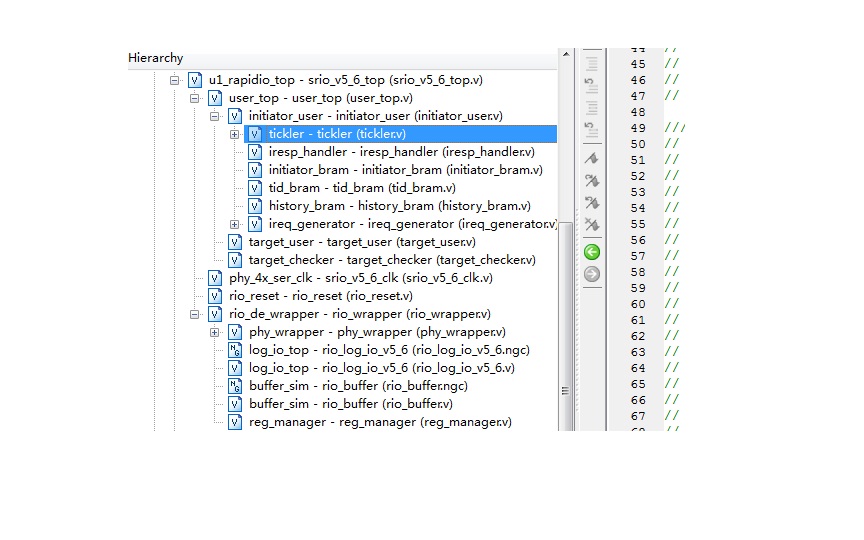

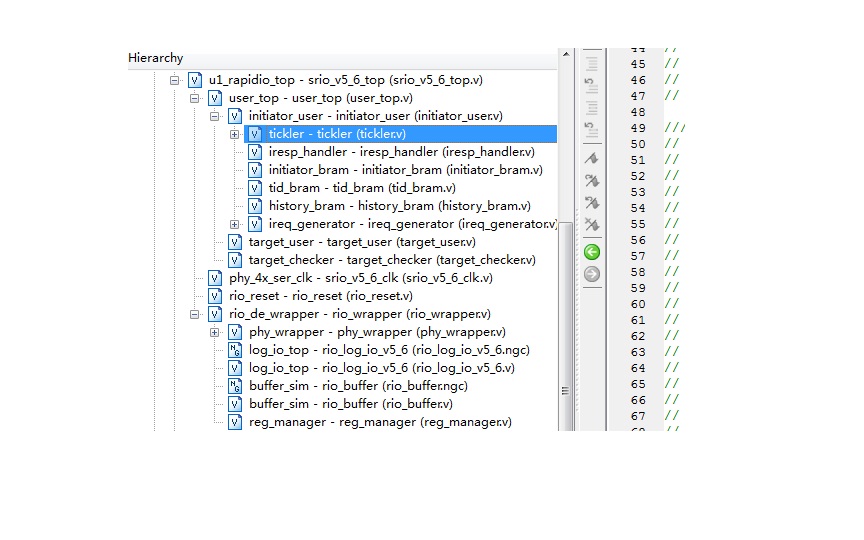

下图是rapido 核的verilog HDL代码目录

rapido 文件目录

待解决的目标:实现DSP和FPGA通信。

1.DSP发送数据到FPGA rapidio核,FPGA从该核中读出数据,传给FPGA下一个模块;

2.上述逆过程FPGA发数据到DSP;

3.上述两个过程“实时”连续传送数据;

求高手指点,之前弄了一段时间,因为时间问题放下了,现在又有时间了,回来重新来过,希望做过的人给些指导啊!

++图里这些代码大致知道作用,现在想知道,如果实现第一个目标,需要去修改哪部分代码?

++rapidio核的接口,只有底层几对rx/tx差分接口,想实现读数据到另一FPGA模块,应该是需要自己写接口吧?

++个人觉得找到解过包的用户数据的RAM,直接来操作这个ram就可以,只是不知道怎么弄?

求助啊,【猴哥】可在,遇到的妖怪搞不定了!!!!!

待解决的目标:实现DSP和FPGA通信。

1.DSP发送数据到FPGA rapidio核,FPGA从该核中读出数据,传给FPGA下一个模块;

2.上述逆过程FPGA发数据到DSP;

3.上述两个过程“实时”连续传送数据;

求高手指点,之前弄了一段时间,因为时间问题放下了,现在又有时间了,回来重新来过,希望做过的人给些指导啊!

++图里这些代码大致知道作用,现在想知道,如果实现第一个目标,需要去修改哪部分代码?

++rapidio核的接口,只有底层几对rx/tx差分接口,想实现读数据到另一FPGA模块,应该是需要自己写接口吧?

++个人觉得找到解过包的用户数据的RAM,直接来操作这个ram就可以,只是不知道怎么弄?

求助啊,【猴哥】可在,遇到的妖怪搞不定了!!!!!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

请看ipcore里面的doc文件夹里面的pdf文档,对接口已经描述的很清楚了,简单说下

srio通信FPGA可以是发起端或响应端,假设fpga和dsp通信,那么dsp给fpga写swrite,那么fpga就是响应段,如果fpga给dsp写swrite,那么fpga就是发起端,可以看看不同模式下的user interface时序,按照文档里面的时序给数据就可以了

收到,谢谢指点,研究中user interface 。。这个“++rapidio核的接口,只有底层几对rx/tx差分接口,想实现读rapidio中数据(DSP传来的数据)到另一FPGA模块”这个该如何操作?

困惑如何了?最好具体点

一周热门 更多>