Xilinx FPGA入门连载49:FPGA片内RAM实例之功能仿真特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

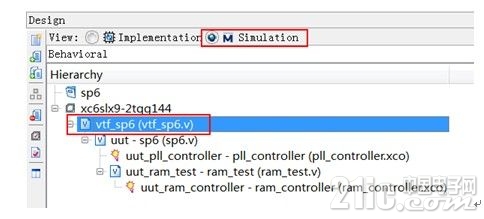

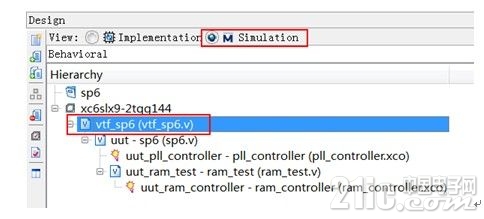

1 Xilinx库设置 打开文件夹sp6ex18下的ISE工程。如图所示,切换到“Design à Simulation”界面。鼠标选中“vtf_sp6.v”文件。

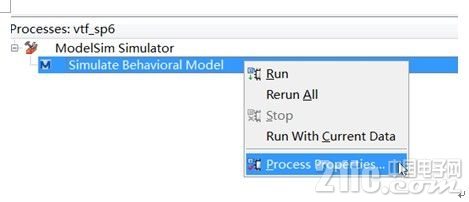

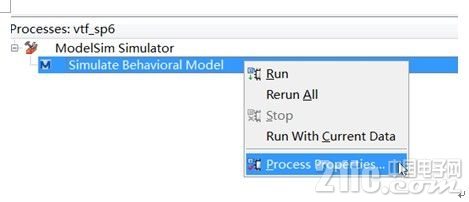

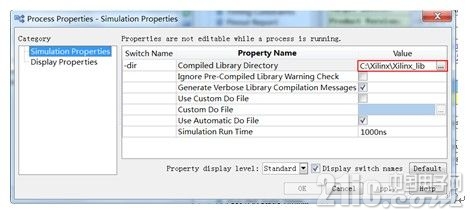

此时,在“Processer:vtf_sp6”下,选择“SimulateBehavioral Model”,然后点击鼠标右键,弹出菜单中选择“ProcessProperties…”。

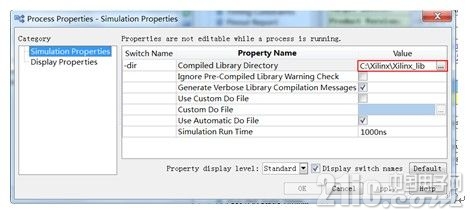

如图所示,确认设置好在安装Modelsim过程中编译好的ISELibrary路径。设定完成后点击“OK”回到ISE主界面。

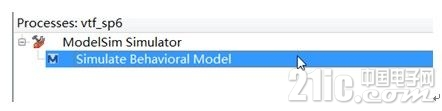

2 功能仿真 如图所示,双击“Simulate Behavioral Model”开始仿真。

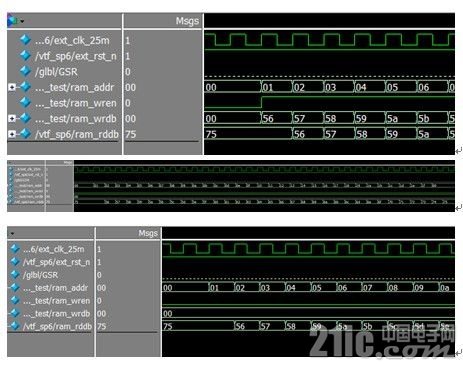

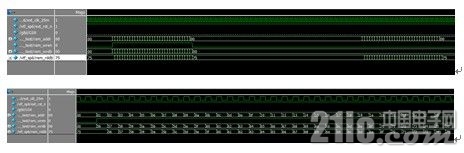

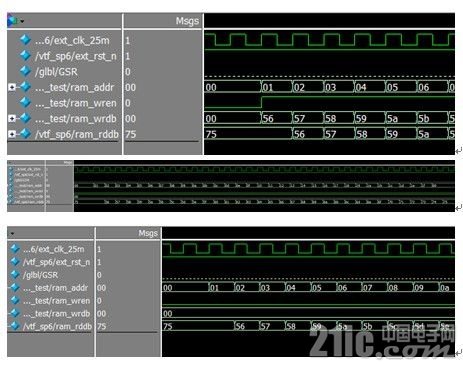

接着,Modelsim中我们可以查看读RAM的波形。

RAM操作的规则大体可以归纳如下:● 写使能信号ram_wren拉高时,当前的地址Ram_addr和写入数据ram_wrdb有效,即ram_addr地址的写入数据ram_wrdb,如波形中往01地址写入数据56、往02地址写入数据57……。● 无论当前的写使能信号ram_wren是否有效,地址ram_addr对应的数据总是在下一个时钟周期出现在读数据总线ram_rddb上,如波形中01地址对应的数据56、02地址对应的数据57……。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>