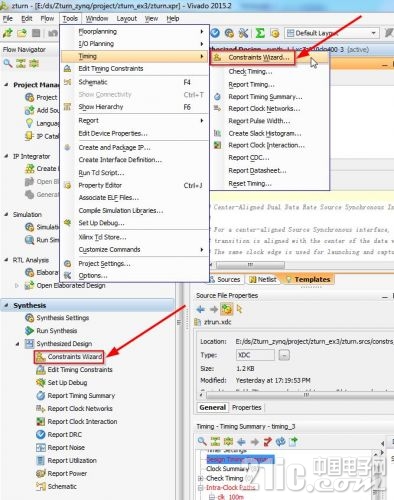

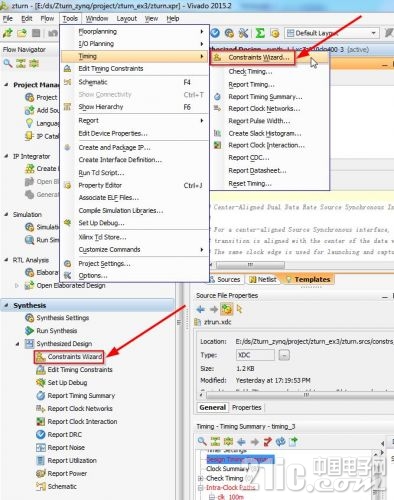

玩转Vivado之Timing Constraints特权同学,版权所有 最近在熟悉Xilinx已经推出好几年的Vivado,虽然特权同学之前已经着手玩过这个新开发工具,但只是简单的玩玩,没有深入,这回得以静下心做些研究,并且纯粹是在Vivado软件的使用方面。最大的感受是,虽然大的框架,基本的流程和方**上没有任何大的变化,不过“换汤不换药”。但是,在工具使用的一些细节上,即用户体验,尤其是易用性方面,能感受到Xilinx下功夫了。 这里就先拿Timing Contrasint方面来做点文章吧。首先是ConstraintsWizard,这里一步一步往下走,几乎所有的Constraint遍历一次,对于第一次做Constraint非常方便。

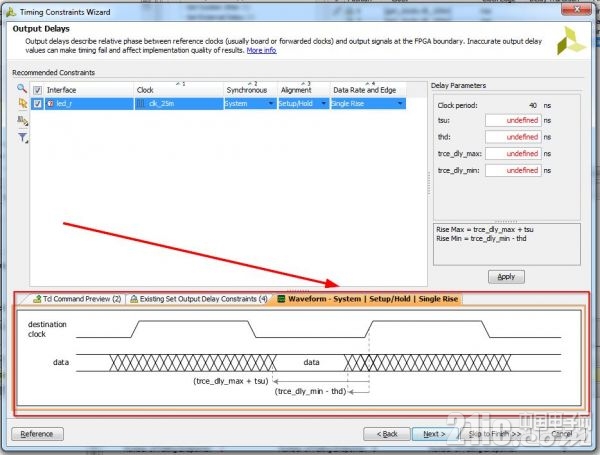

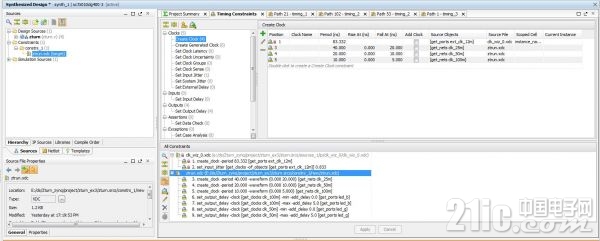

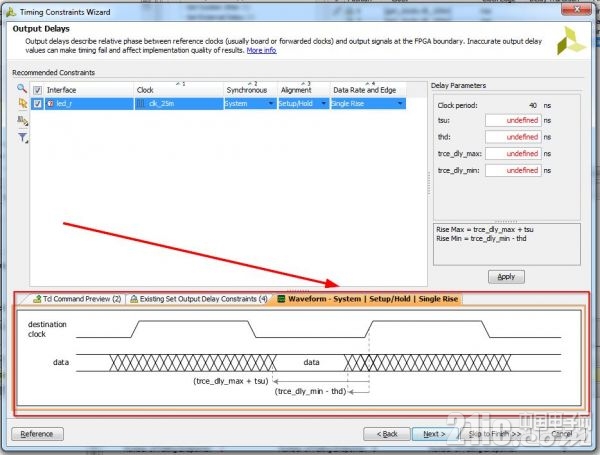

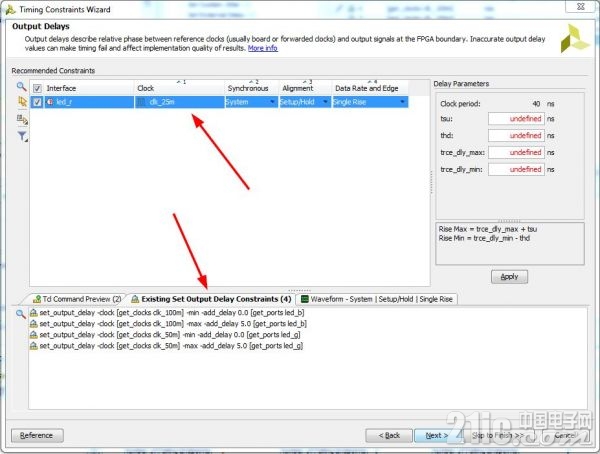

图1 ConstraintsWizard开启按钮 对于Constraints Wizard中input/output端口的约束,过去特权同学一到具体给定约束值时,老是范糊涂,因为Quartus II和ISE对IO端口的约束方式和计算公式略有不同,容易混淆。而老掉牙的ISE中也只是光秃秃的没有任何提示,Vivado可好了,出现了标好了具体约束值的时序图,一目了然,很容易就可以下手做约束了。

图2 Constraints Wizard的output约束界面

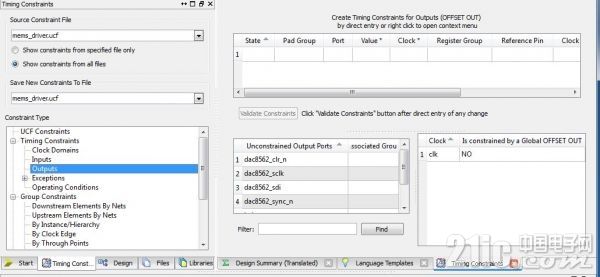

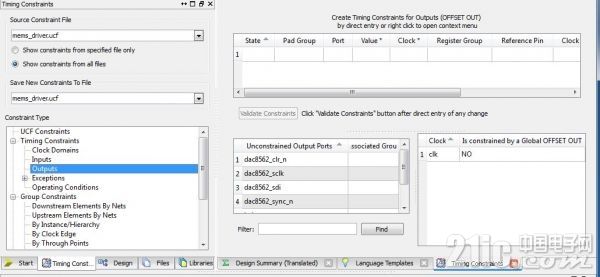

图3 ISE中光秃秃的Constraint界面 另外一点,Xilinx一直做得比Altera的TimeQuest好的是,对于IO端口约束过的和没有约束过的,都能够一目了然的分别列出来,让设计者不至于遗漏。

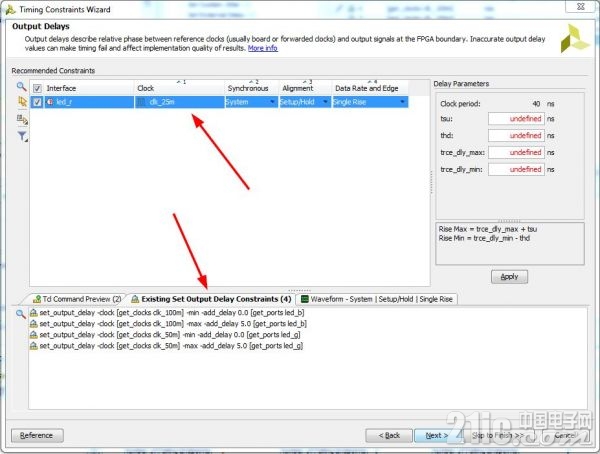

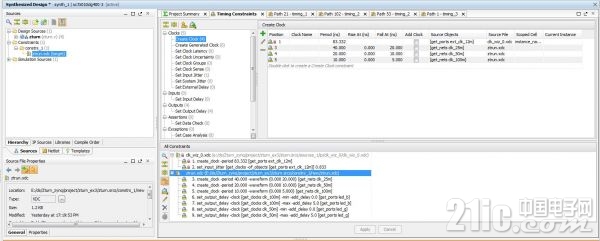

图5 ConstraintsWizard的output约束界面 当然了,除了ConstraintsWizard,还是有专门的Timing Constraints页面可以查看、编辑所有的约束。与以前的UCF文件不一样的是,Vivado用新的格式XDC用于存储约束脚本。

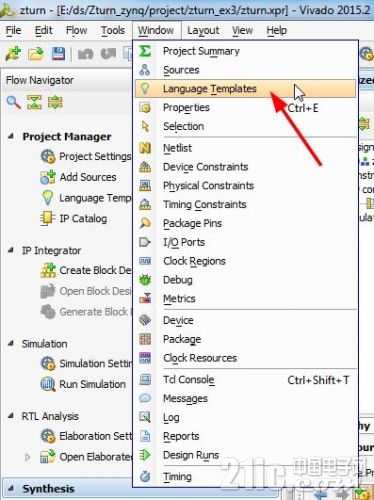

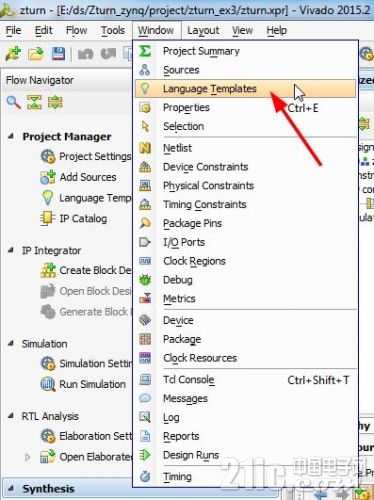

图6 TimingConstraints页面 另外,特权同学还发现了一个非常好的功能,即约束模版(Language Templates)中的XDC模版。

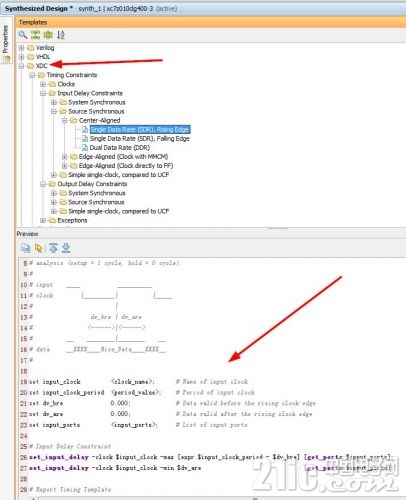

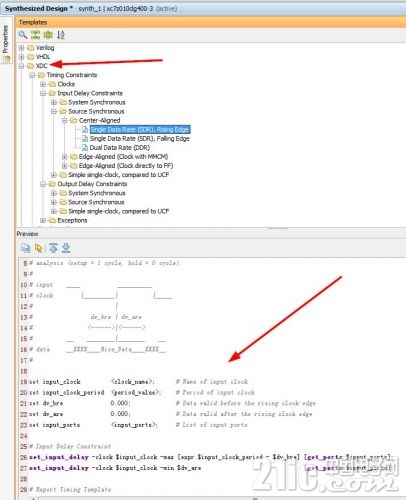

图7 LanguageTemplates开启按钮 Language Templates中,ISE也有时序约束的模版,但是比较下来,发现Vivado中增加了很多实用的模型,比如图8所示的Center-Aligned --> Single Data Rate(SDR),里面有时序示意图,非常简单清晰,对于这类常用接口不需要再去研究input/output端口时序约束公式了,直接上来就可以填时间,然后copy到工程的XDC文件中。

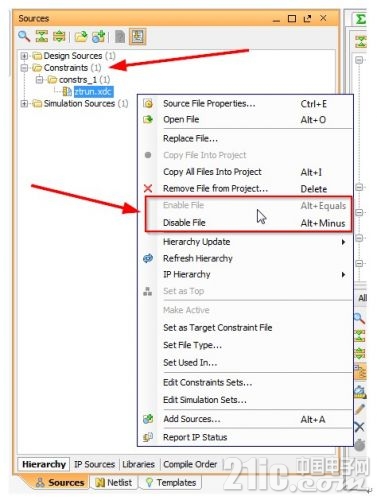

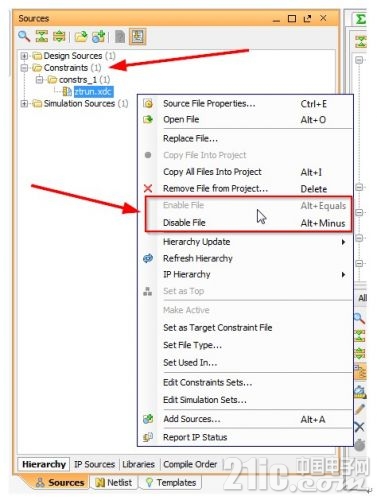

图8 LanguageTemplates页面 再说XDC文件的管理,它其实不光可以存储时序约束脚本,所有相关的设计约束脚本都是存储在XDC格式的文件中。而且可以有多个XDC文件同时存在一个工程中,它们可以Enable也可以Disable。对于一个难于收敛的时序设计,这个Enable和Disable功能就非常实用了。设计者通常会使用不同的约束策略,过去只能在一个文件里面改来改去,注释来注释去,极易混淆,但是这种多文件管理的支持,就非常便于管理和维护。

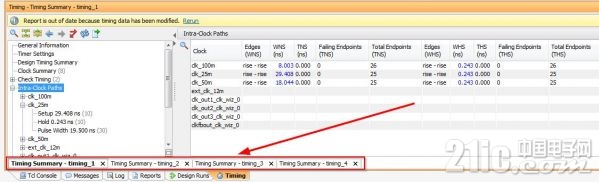

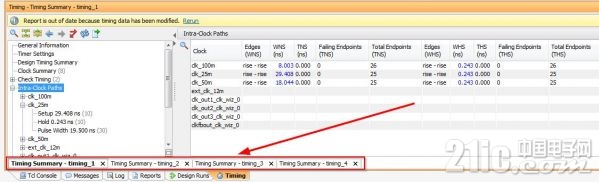

对于同一个工程,甚至可以同时查看不同约束策略下的时序报告,可以非常直观的对比。这一点在过去的ISE上咱没有试过,不知道可不可以,但是在Quartus II的TimeQuest中肯定不能,所以,这绝对又是一个亮点。

一周热门 更多>