Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

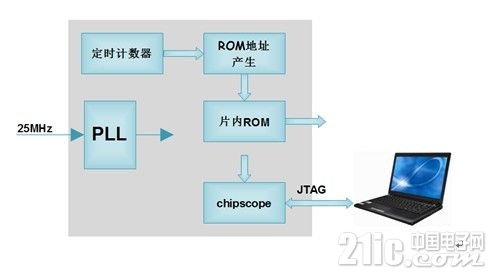

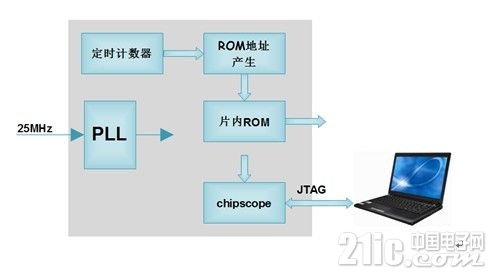

1 功能概述 该工程实例内部系统功能框图如图所示。我们通过IP核例化一个ROM,定时遍历读取其所有地址的数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察ROM的读时序。

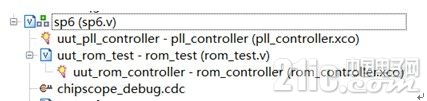

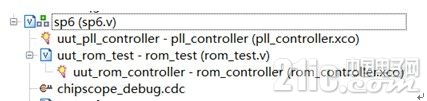

2 模块划分 本实例工程模块层次如图所示。

● Pll_controller.v模块产生FPGA内部所需时钟信号。● Rom_test.v模块例化FPGA片内ROM,并产生FPGA片内ROM读地址,定时遍历读取ROM中的数据。● Chipscope_debug.cdc模块引出ROM的读取信号总线,通过chipscope在ISE中在线查看ROM读取时序。

一周热门 更多>