Xilinx FPGA入门连载28:基于Chipscope的超声波测距调试之Chipscope配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

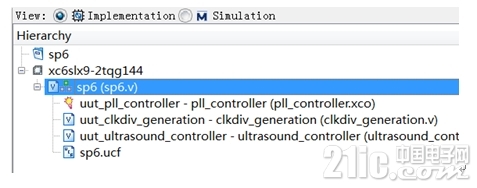

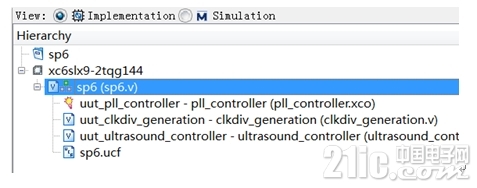

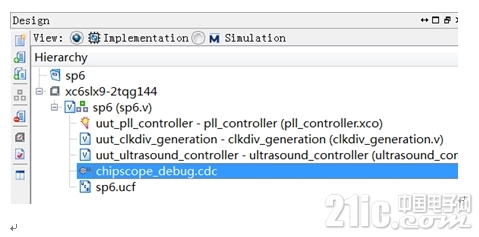

1 工程移植 可以复制上一个实例sp6ex9的整个工程文件夹,更名为sp6ex10。然后在ISE中打开这个新的工程。接着将这个工程的各个功能模块代码输入的相应的设计文件中。除了chipscope功能,这个工程的代码层次如下所示。

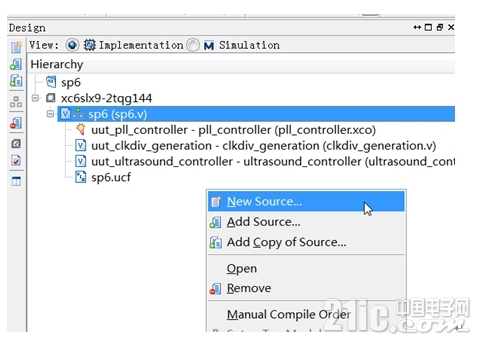

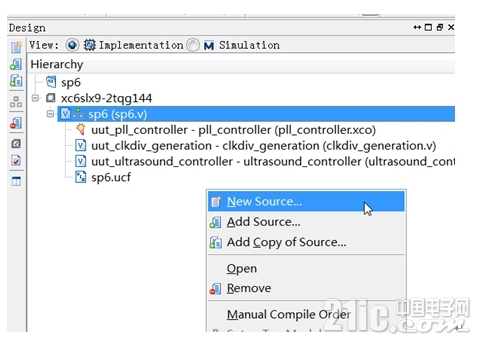

2 新建文件 如图所示,在“Design à Implementation”下的任意空白处单击鼠标右键,弹出菜单中选择“New Source …”。

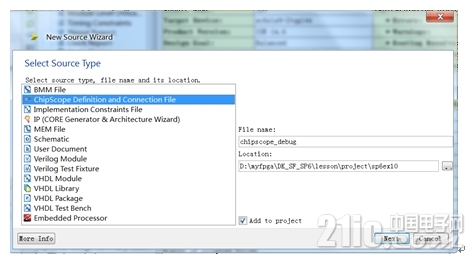

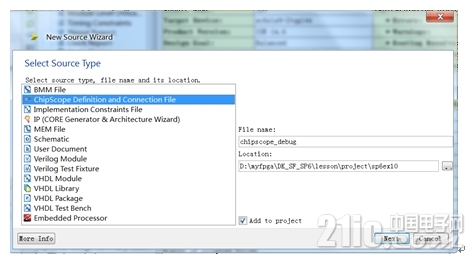

在弹出的“New Source Wizard à Select Source Type”下,如图所示,选择文件类型为“ChipScope Definition and Connection file”。“File name”可以给新创建的文件取个名字,我们命名为“chipscope_debug”。“Location”即生成的新文件所有相关源文件的存储路径,默认即为当前工程路径下,通常我们不需要更改它。点击“Next”继续。

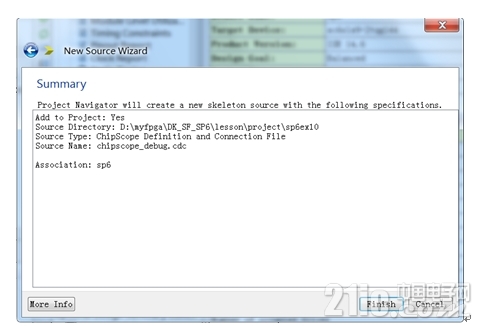

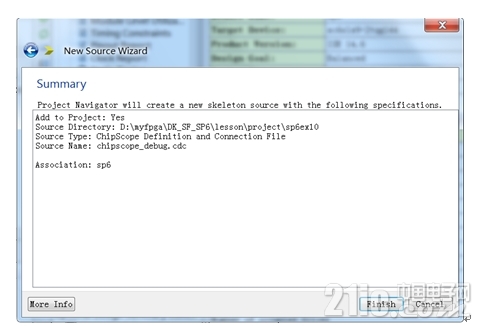

如图所示,前面的配置信息在“New Source Wizard à Summary”页面重新罗列供review。点击“Finish”继续。

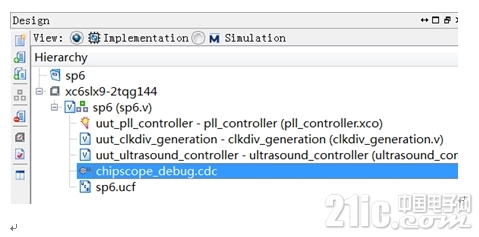

随后,我们可以看到代码层次结构中多了一个名为“chipscope_debug.cdc”的文件,如图所示。

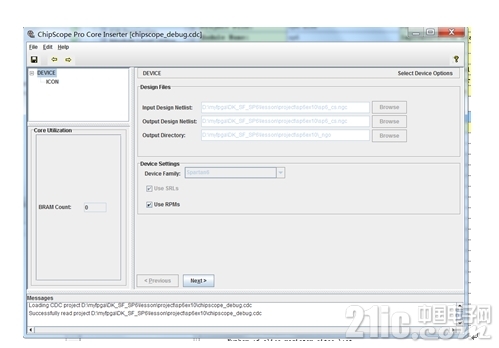

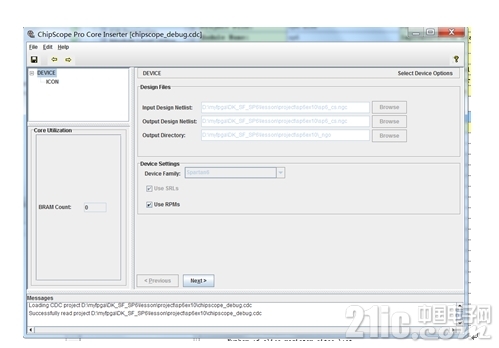

3 Chipscope配置 双击“chipscope_debug.cdc”文件,可以进行chipscope基本参数的配置。 第1个页面,如图所示,不需要我们做任何设置,都是一些默认不可更改的信息。点击“Next”继续。

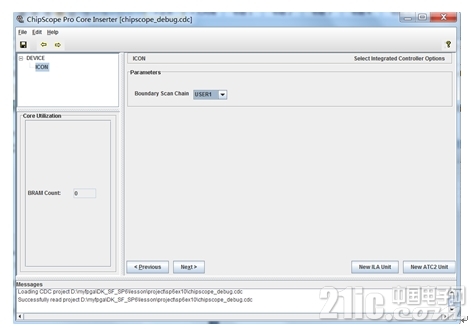

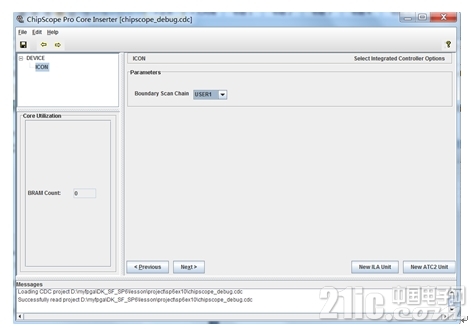

第2个页面,也不需要做设置,如图所示,继续点击“Next”。

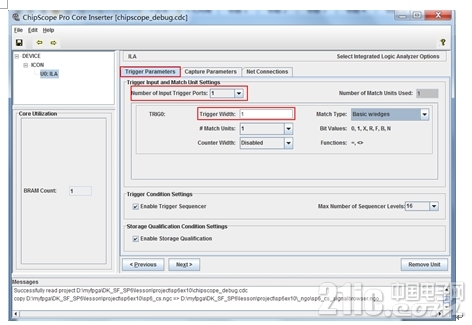

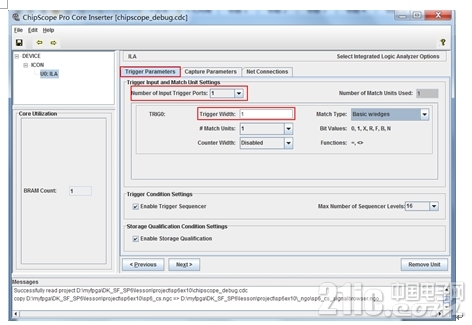

第3个页面,“Trigger Parameters”页面,如图所示,“Number of Input Trigger Ports”可以设置触发端口(或者通道)数量,我们选择“1”,随后在“Trigger Width”即触发位宽上我们也设置“1”。“Match Type”即触发类型我们选择“Basic w/edges”。这里简单的说明一下,每一个Trigger Ports都可以有最多16bit的位宽,我们可以设置多个Trigger Ports,不同Trigger Ports之间也可以进行丰富的各种组合触发方式,这较之普通的逻辑分析仪要灵活很多。

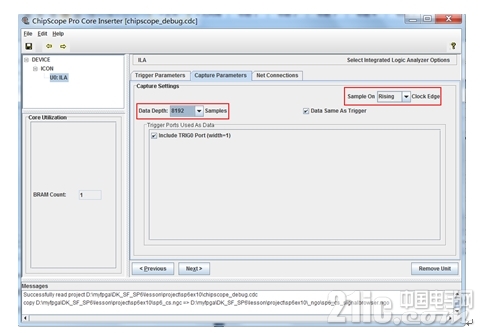

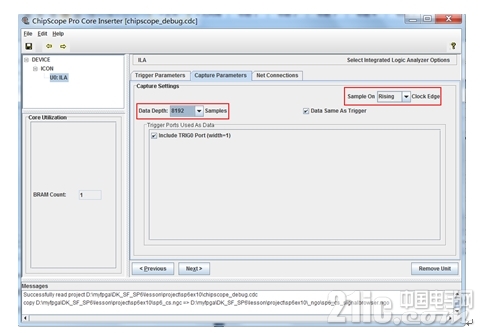

第4个页面,“Capture Parameters”页面,如图所示,设置“Data Depth”,即采样深度为8192,这个采样深度虽然越大越有利于调试,但是必须考虑FPGA片内的存储器资源情况,若设置的深度导致总存储量超过FPGA资源,则无法通过编译。“Sample On”选择“Rising Clock Edge”,即上升沿触发。

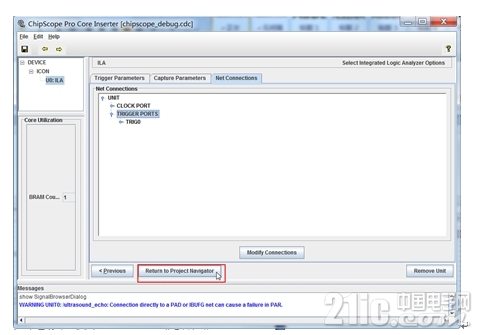

第5个页面,“Net Connections”页面,如图所示。这里可以选择采样时钟和触发或采样信号。点击界面下方的“Modify Connections”。

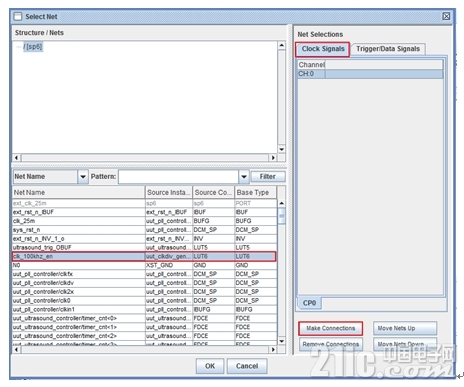

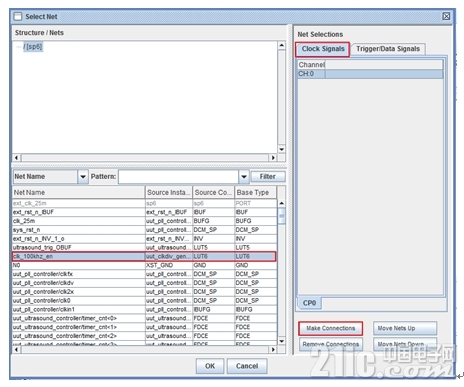

采样时钟的匹配,如图所示,我们可以做以下3步完成信号的匹配。在右上方的“NetSelections”下面选中“Clock Signals”,然后找到左下方“Net name”为“clk_100khz_en”的信号,选中它,最后点击右下方的“Make Connections”按钮。

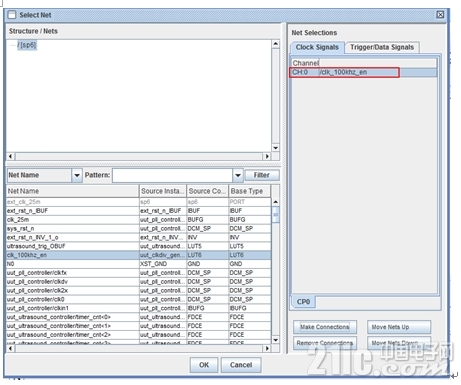

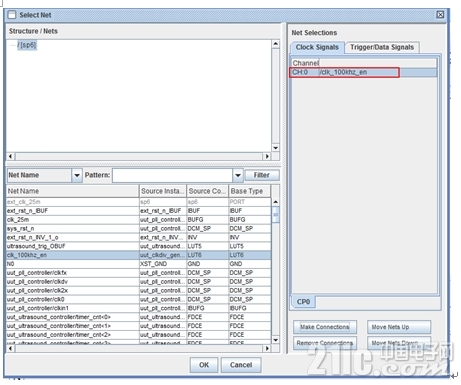

如图所示,完成上面的时钟匹配后,clk_100khz_en信号就出现在了“ClockSignals”下方的“CH:0”的右侧,说明采样时钟的匹配已经完成。

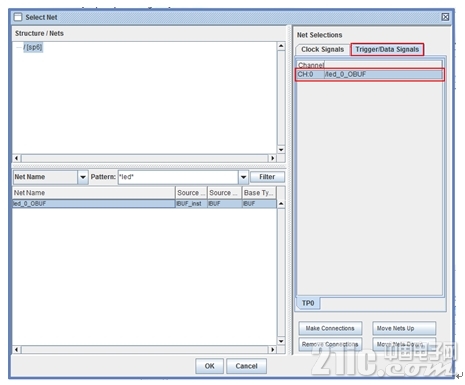

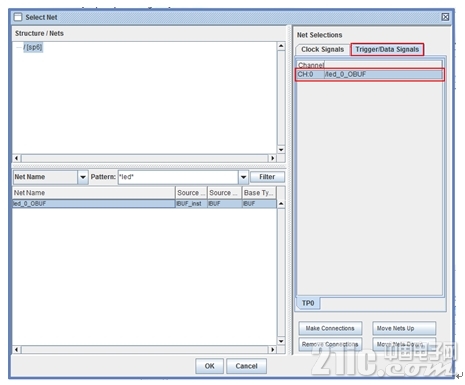

同样的方式,如图所示,我们把led_0_OBUF(即信号ultrasound_echo)信号添加到“Trigger/Data Signals”中。完成匹配后,点击“OK”。

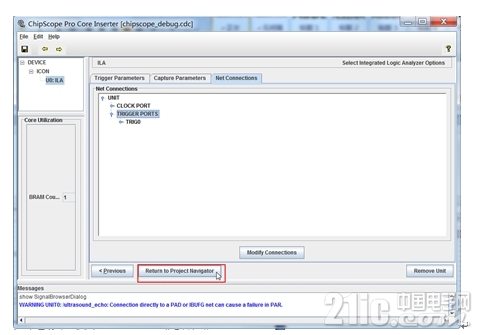

如图所示,回到主页面,点击“Return to Project Navigator”完成设置。

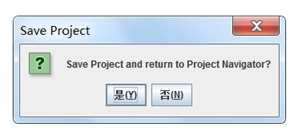

随后会弹出如下图所示的对话框,点击“是”。

回到ISE中,双击“GenerateProgramming File”对整个工程进行编译。

一周热门 更多>