Xilinx FPGA入门连载27:基于Chipscope的超声波测距调试之功能简介特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

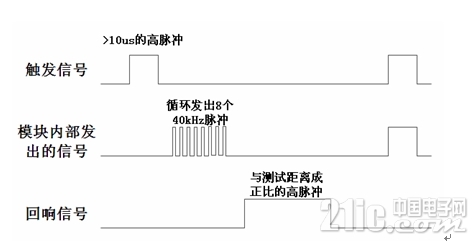

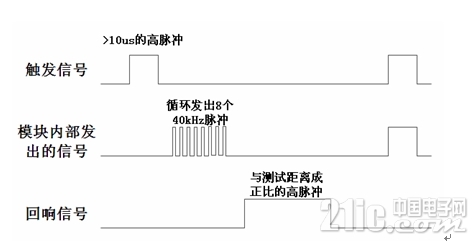

1 超声波测距原理超声波模块的驱动控制原理很简单。如图所示,我们用FPGA产生一个大于10us的触发信号(TRIG)给超声波模块,超声波模块内部会产生一些脉冲信号,经过内部的滤波处理,最终他反应到与FPGA连接的输出回响信号(ECHO)上则是一个高脉冲信号。这个高脉冲信号的宽度通过一个公式换算后就能够获得当前障碍物和模块间的距离。

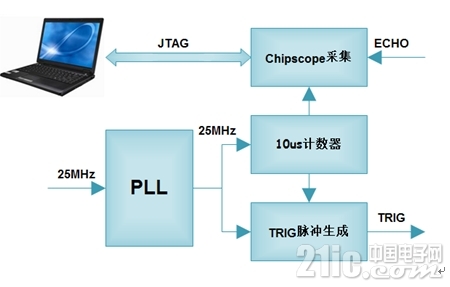

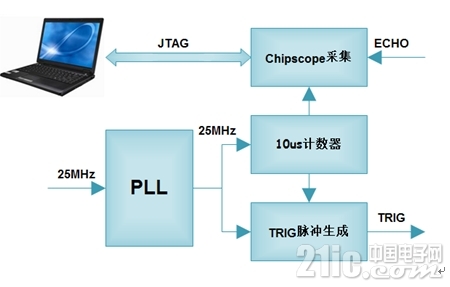

该超声波模块的有效测试距离为2cm~400cm,测距精度可以达到2mm。假设超声波模块与障碍物间的距离为S(单位:m),ECHO输出的高脉冲宽度为T(单位:s),声速在25°C条件下定义为346(单位:m/s)。那么ECHO脉冲宽度与测试距离的关系如下。 S = (T*346)/2 通过这个公式,我们就可以使用回采的ECHO脉冲信号持续时间,换算出障碍物与超声波测距模块之间的距离。 2 功能简介 本实例的功能框图如下所示。25MHz时钟来自PLL,它作为内部产生10us分频计数逻辑的基频时钟。10us脉冲直接输出到超声波测距模块的TRIG端口;用10us的时钟频率取采集超声波测距模块的回响信号ECHO,它通过Chipscope内嵌逻辑分析仪来观察脉冲变化。Chipscope内嵌逻辑分析仪则是通过JTAG线缆连接到PC的ISE软件中查看信号波形。

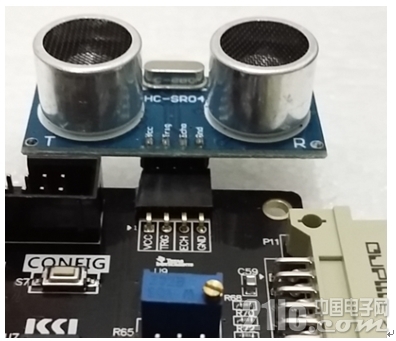

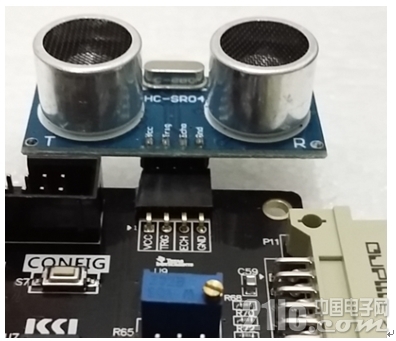

3 硬件装配 和其他实例不同,本实例的超声波测距模块需要和我们的板子进行装配连接。如图所示,在SF-SP6开发板的右上角插座P7用于连接超声波模块。

一周热门 更多>