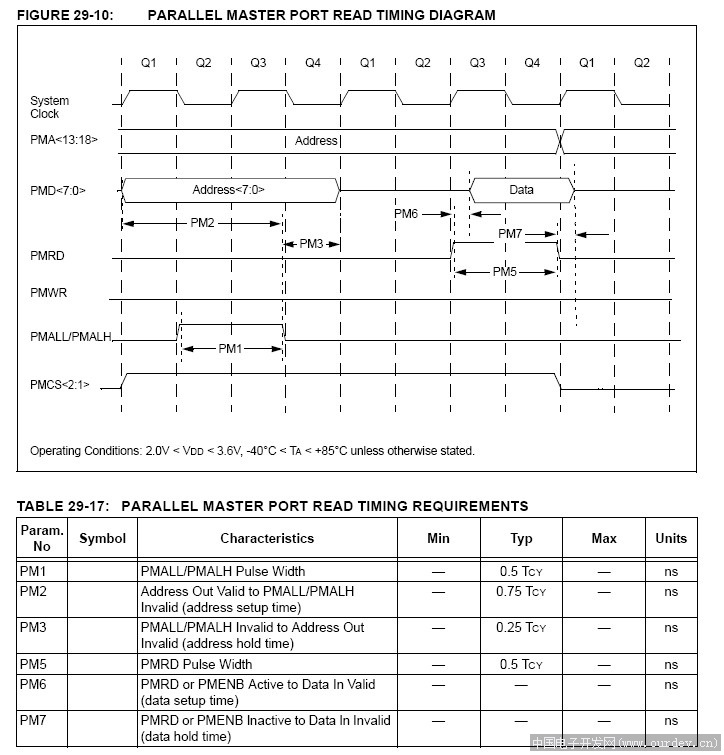

PIC18F46J50外部总线读时序如下:

(原文件名:sa.jpg)

问题是:MCU在何时取总线上的数据?并且对PM6的时间也没有作出明确的规定?按照以上的描述,难道把时序描述清楚了吗?

另外一个问题:

按照时序的描述在ALE的上升沿锁存数据,但是发现不对;用示波器观察后,发现地址和锁存信号差不多是同时有效的;这跟时序的描述相差很大,按照他的描述正常情况下,在读周期开始总线上的地址就有效了(CS和地址基本上同时有效),但是实际上是在CS有效的1/4周期后地址才有效果,也就是在图中所描述的Q2开始有效果,有效时间也是0.5TCY,而在时候锁存信号也开始上升,在这时获得地址肯定是存在不稳定的.

在ALL的下降沿锁存地址,算是正常了;但是现在情况是TCY=1us;FPGA在时间上肯定是充足的;TCY最快能到(1/12)us,差不错80ns;这样的话PM3差不多就剩20ns(正常情况,PM3=0.25TCY),并且它对最小值也没有说.这改怎么办?

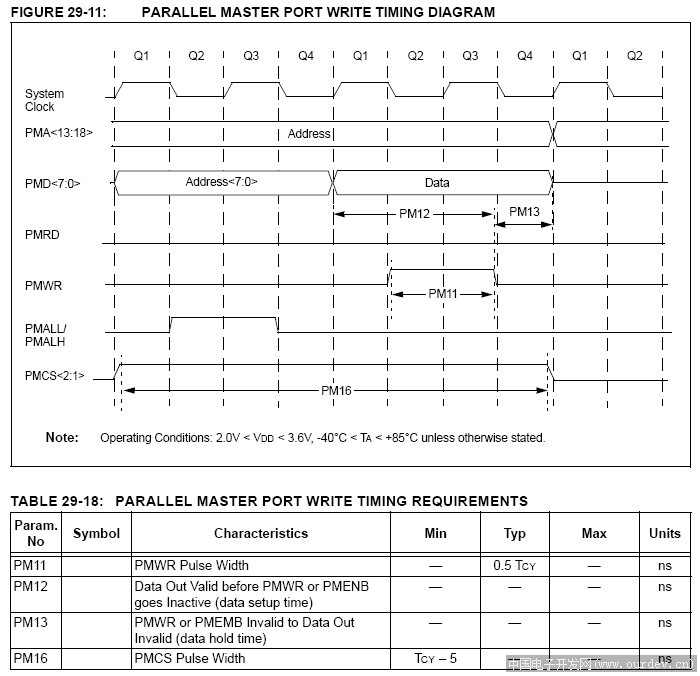

不知道有没有用过这个IC的朋友.以下是写时序.

(原文件名:ds.jpg)

同样的对一些并没有描述清楚.写时序用示波器看了之后地址和ALL也存在以上描述的情况.只说了个典型值,对最坏情况都没有说明.

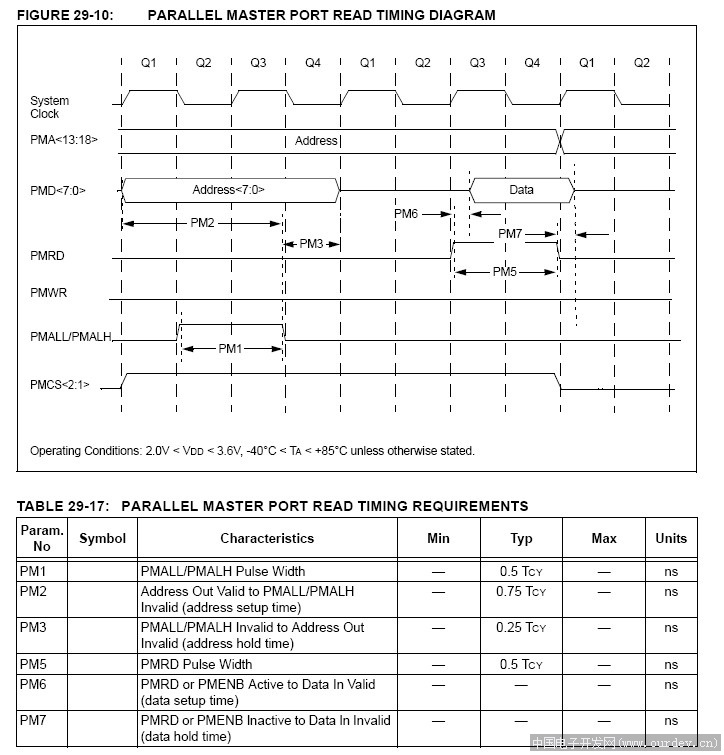

(原文件名:sa.jpg)

问题是:MCU在何时取总线上的数据?并且对PM6的时间也没有作出明确的规定?按照以上的描述,难道把时序描述清楚了吗?

另外一个问题:

按照时序的描述在ALE的上升沿锁存数据,但是发现不对;用示波器观察后,发现地址和锁存信号差不多是同时有效的;这跟时序的描述相差很大,按照他的描述正常情况下,在读周期开始总线上的地址就有效了(CS和地址基本上同时有效),但是实际上是在CS有效的1/4周期后地址才有效果,也就是在图中所描述的Q2开始有效果,有效时间也是0.5TCY,而在时候锁存信号也开始上升,在这时获得地址肯定是存在不稳定的.

在ALL的下降沿锁存地址,算是正常了;但是现在情况是TCY=1us;FPGA在时间上肯定是充足的;TCY最快能到(1/12)us,差不错80ns;这样的话PM3差不多就剩20ns(正常情况,PM3=0.25TCY),并且它对最小值也没有说.这改怎么办?

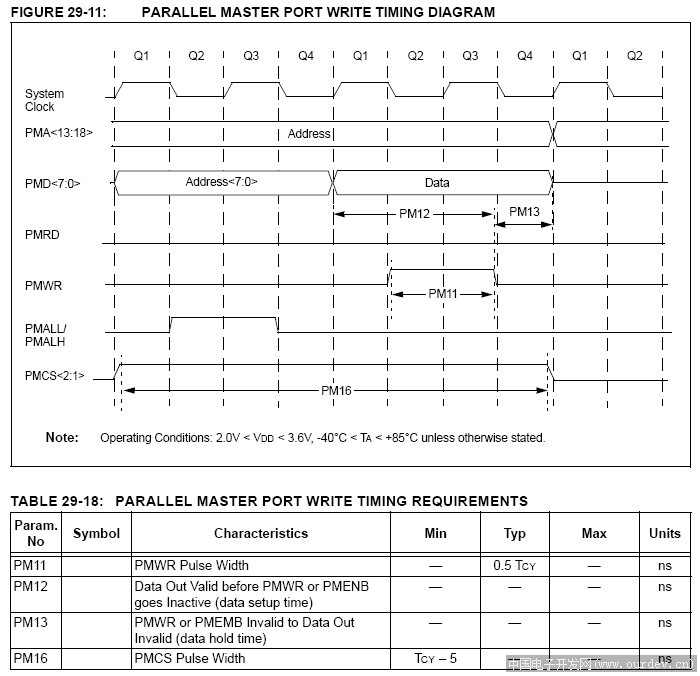

不知道有没有用过这个IC的朋友.以下是写时序.

(原文件名:ds.jpg)

同样的对一些并没有描述清楚.写时序用示波器看了之后地址和ALL也存在以上描述的情况.只说了个典型值,对最坏情况都没有说明.

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>