使用TI的16位DAC(DAC8831)和FPGA进行SPI通信,SPI时钟速率50MhzDAC参考电压Vref=4.096V,采用TI的ref5040作为外部参考电压,后面经过一个运放跟随作为缓冲向DAC输出参考电压,

DAC输出端口输出0~Vref对应0x0000~0xFFFF

FPGA持续发出0x0000 理论应该输出为0V,实际输出平均12.6mV,峰峰值压差123mV

持续发出0x7FFF 理论输出应该为2.048V,实际平均输出2.0527V,峰峰值压差250mV

持续发出0xFFFF,理论应该输出为Vref=4.096V,实际输出平均值为4.0802V,峰峰值157mV

FPGA向DAC发出 0x0F0F ,理论输出

理论上,DAC输出端口电压应该为 240.941mV,实际平均值256.6mV,峰峰压差193mV

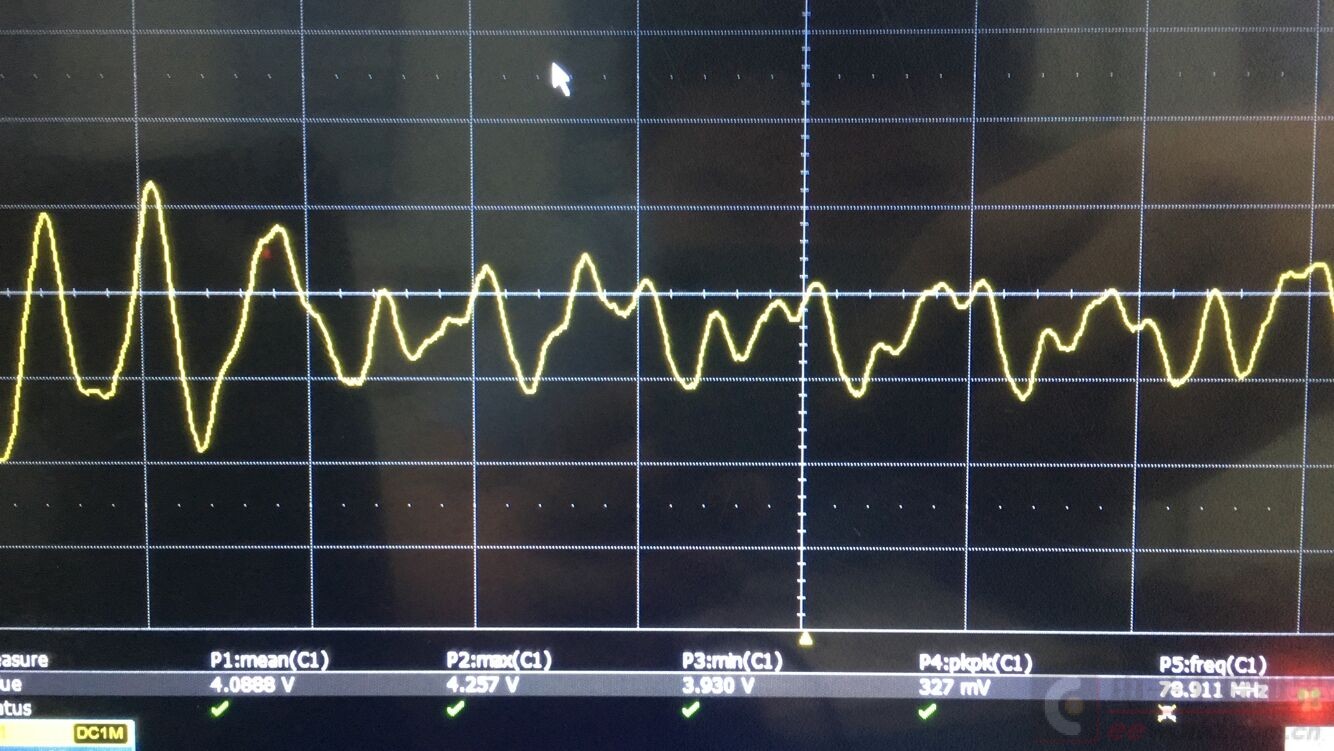

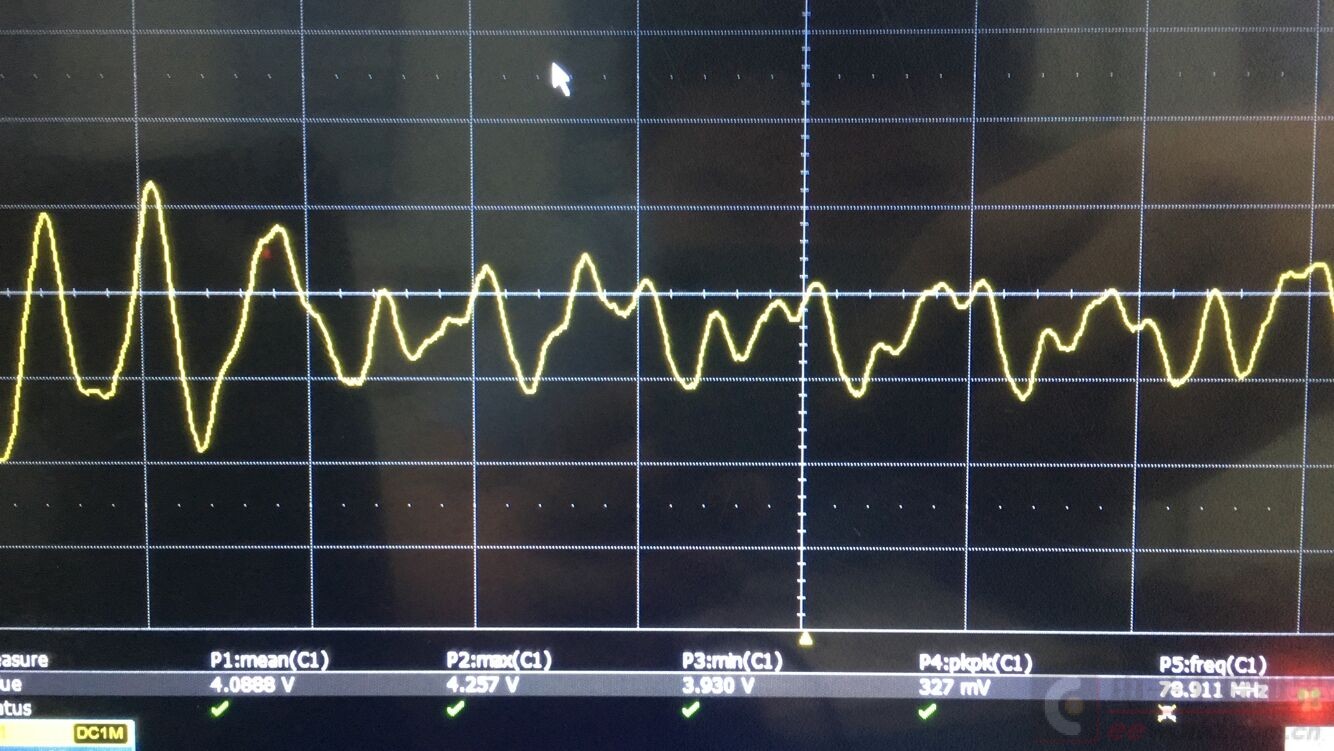

参考电压用示波器测量的结果是,平均值4.0888V,峰峰值压差327mV

这个DAC输出太不稳定了,经过分析,我认为是参考电压Vref不稳定导致的DAC输出不稳定,有没有什么其他的建议,怎么让参考电压稳定?或者怎么让输出DAC输出稳定?

此帖出自小平头技术问答

DAC输出端口输出0~Vref对应0x0000~0xFFFF

FPGA持续发出0x0000 理论应该输出为0V,实际输出平均12.6mV,峰峰值压差123mV

持续发出0x7FFF 理论输出应该为2.048V,实际平均输出2.0527V,峰峰值压差250mV

持续发出0xFFFF,理论应该输出为Vref=4.096V,实际输出平均值为4.0802V,峰峰值157mV

FPGA向DAC发出 0x0F0F ,理论输出

理论上,DAC输出端口电压应该为 240.941mV,实际平均值256.6mV,峰峰压差193mV

参考电压用示波器测量的结果是,平均值4.0888V,峰峰值压差327mV

这个DAC输出太不稳定了,经过分析,我认为是参考电压Vref不稳定导致的DAC输出不稳定,有没有什么其他的建议,怎么让参考电压稳定?或者怎么让输出DAC输出稳定?

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

根据什么现像,你这么认为?

既然有很好的示波器,直接用示波器看看基准电压。

从示波器图片中看不出横轴(时间)每格是多少。

猜测:电路板布线不当造成的干扰。

5040已经是非常好非常好的参考源,难道你买的假货?

应该不是假货吧。。淘宝上某大型芯片商城买的。

刚刚单独把一个新的芯片焊接到一个空板子上,通上电源,电源是平均6.9311V,峰峰值压差63mV,如下图

测试的REF5040输出为平均4.0903V,峰峰值压差60mV,如下图

测试电路的原理图如下:

应该怎么看输出稳定不稳定呢?从示波器上看,这个波动频率特别高,几Mhz。而我的输入也有几十Mhz的波动频率。

根据数据手册上的电源抑制比PSRR的图像,

到10khz以上,电源抑制比就很低了,会是这个原因导致输出电压的纹波过大吗?

测试电压基准,估计你们实验室里面的仪器设备办不到——没有那么高的精度。

从“波动频率特别高”这句看,更像是引入了干扰。至于干扰是布线不合理造成的,还是电源不干净造成的,还是外界通过空间耦合的,难以判断。

一周热门 更多>