Xilinx FPGA入门连载12:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

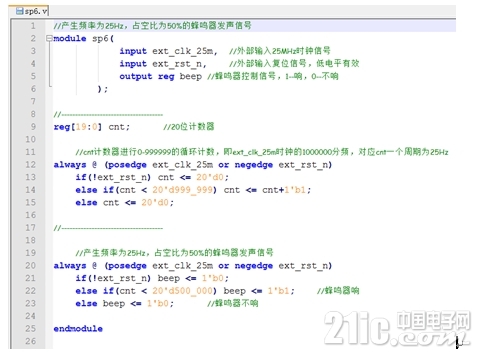

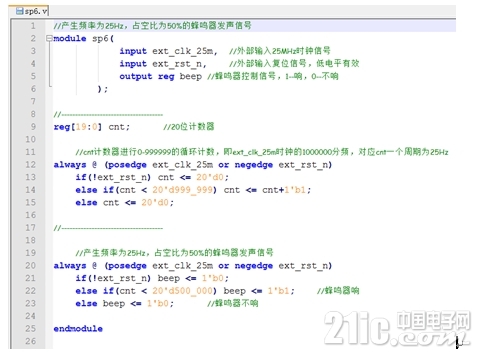

1 工程移植 复制sp6ex1整个文件夹,将其更名为sp6ex2。然后我们打开“…sp6ex2source_code”文件夹下的sp6.v源代码文件。 删除sp6.v文件原有的代码,将上一个lesson的源码整个复制进去。如图所示。

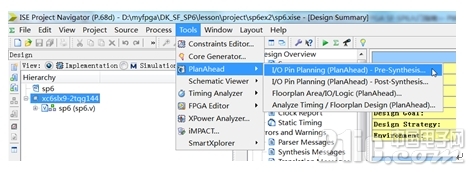

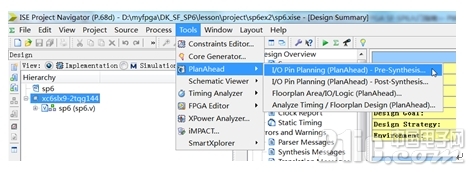

接着使用ISE打开刚刚移植好的sp6ex2文件夹下的工程。 2 PlanAead引脚分配 这个例程的顶层源码里有3个接口,即: input ext_clk_25m, //外部输入25MHz时钟信号 input ext_rst_n, //外部输入复位信号,低电平有效 output reg beep //蜂鸣器控制信号,1--响,0--不响 这3个信号都是FPGA引脚上定义和外部设备连接的信号,因此我们需要将这些信号和FPGA的引脚进行映射。 如图所示,点击ISE菜单上的“Tools à PlanAhead à I/O Pin Planning(PlanAhead) – Pre-Synthesis…”选项。

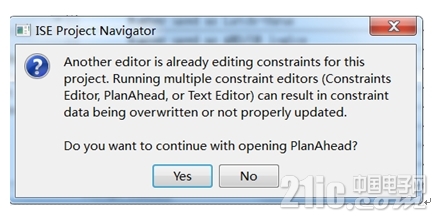

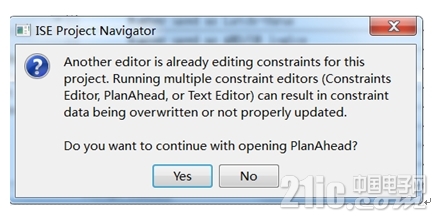

若弹出如下菜单,点击“Yes”继续。

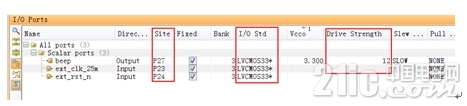

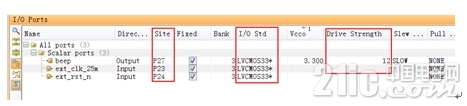

如图所示,在PlanAead界面最下面出现了“I/O Ports”列表中,有我们的3个信号接口,这里“Site”一列可以输入它们对应FPGA的引脚;“I/O Std”一列可以输入I/O电平标准;对于输出信号,“Drive Strength”一列还可以设置输出驱动电流强度。

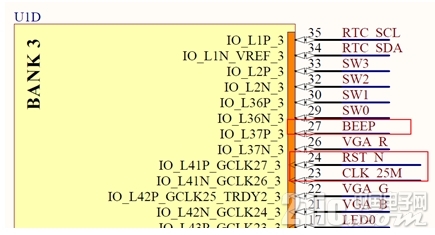

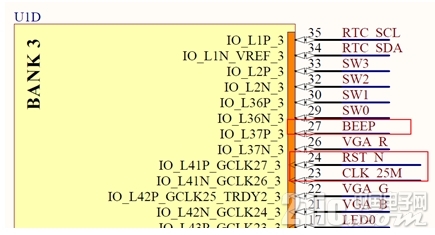

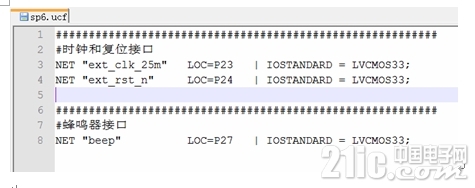

查看SF-SP6开发板的原理图,如图所示,这里BEEP对应FPGA引脚号是27,那么前面我们就在Site列输入P27;RST_N和CLK_25M分别为24和23,则输入P24和P23。

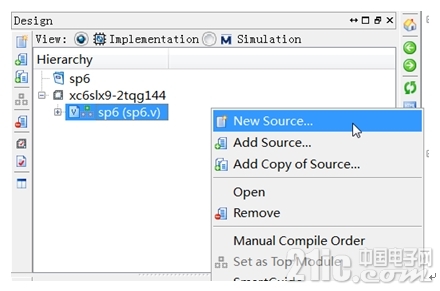

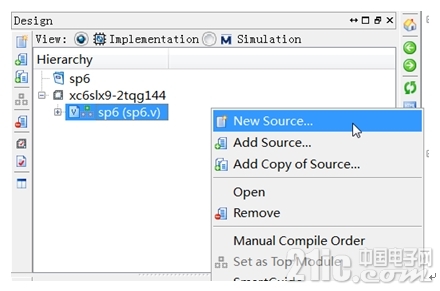

完成分配后,别忘记保存后退出PlanAead界面。 3 脚本直接引脚分配 除了使用PlanAead这种图形界面方式分配引脚,也可以直接使用脚本语法分配引脚。下面先新建这个脚本文件,即ucf文件,我们前面在PlanAead界面分配的引脚信息也会存储在这个ucf文件中。 在“Design àImplementation à Hierarchy”的任意空白处单击右键,选择“NewSource…”,如图所示。

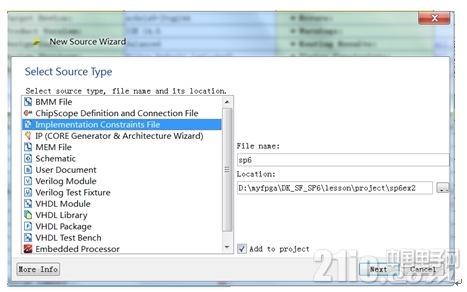

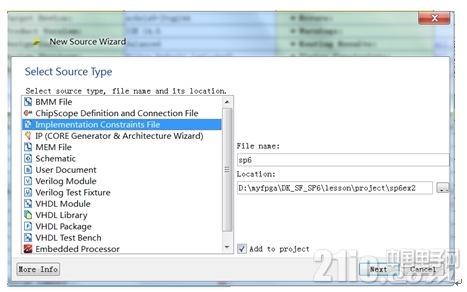

如图所示,选择“Implementation Contraints File”,输入文件名和路径,然后点击“Next”。

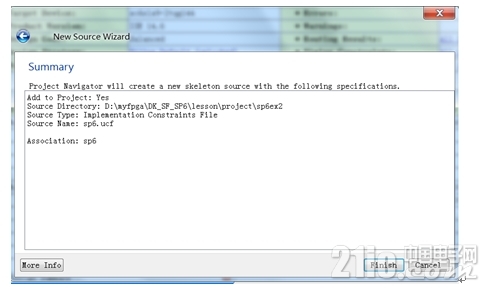

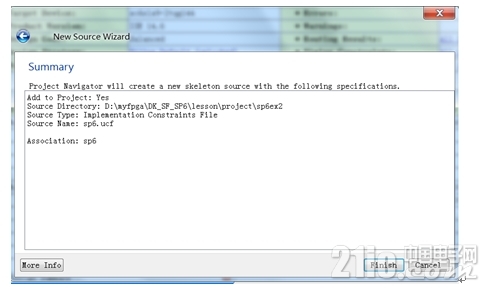

接着弹出报告,点击“Finish”完成创建。

如图所示,此时的sp6.v下面多了一个sp6.ucf文件,选中它,接着在Processes下面双击“EditConstraints(Text)”。

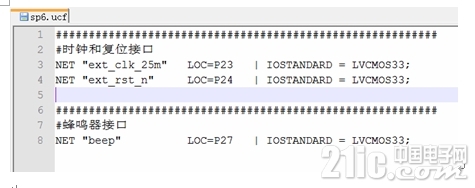

ISE会调用Notepad++打开sp6.ucf文件,如图所示,这里的脚本和我们前面使用PlanAhead进行的引脚分配约束是一样的。

一周热门 更多>