Xilinx FPGA入门连载5:ISE与Modelsim联合仿真之库编译特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

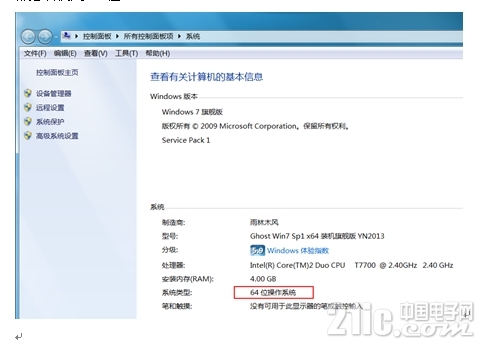

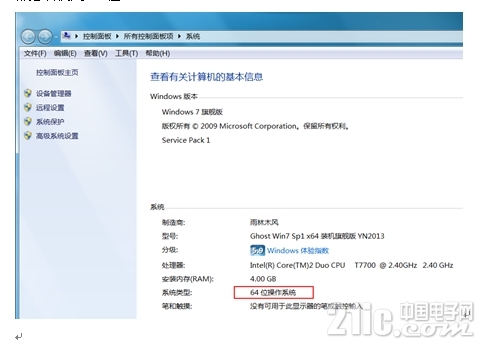

1 操作系统确认 由于我们在安装ISE时,同时安装上了32位和64位对应的ISE。而在实际使用中,我们建议大家配合自己PC的操作系统来使用。如何确认自己的操作系统位数呢?很简单,如图所示,以WIN7操作系统为例,在电脑桌面的“计算机”图标上单击右键,弹出菜单中选择“属性”。

如图所示,弹出的系统窗口中,“系统类型”一栏将显示操作系统的位数,如笔者使用的操作系统为64位。因此,接下来的所有涉及到32位和64位操作系统选择的选项,我们都必须使用64位。

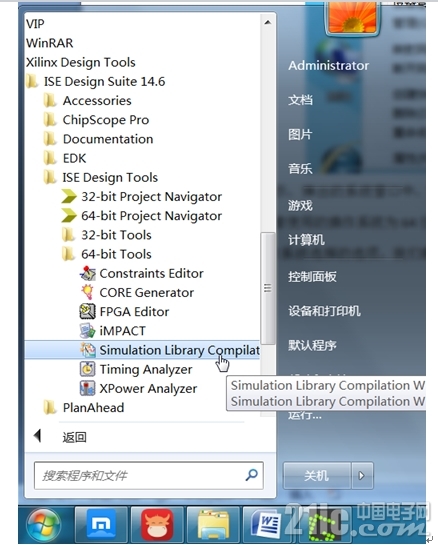

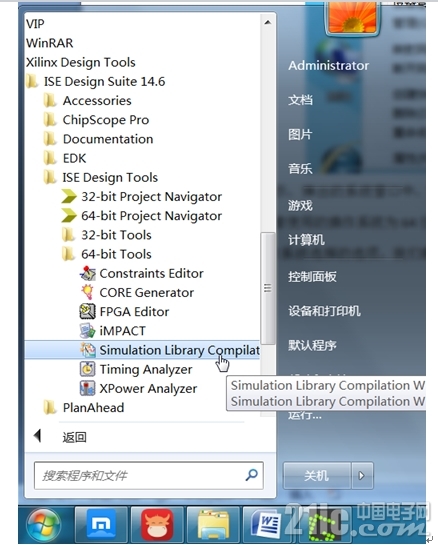

2 Xilinx库编译 在开始菜单中,找到如图所示的“Xilinx Design Tools à ISE Design Suite 14.6 à ISE Design Tools à 64-bit Tools à Simulation Library Complication Wizard”选项,点击打开。

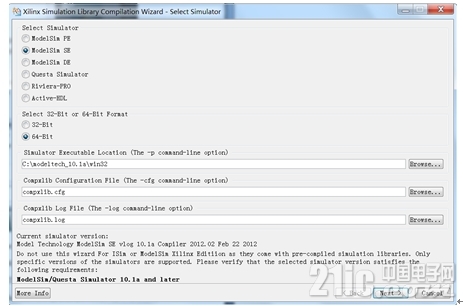

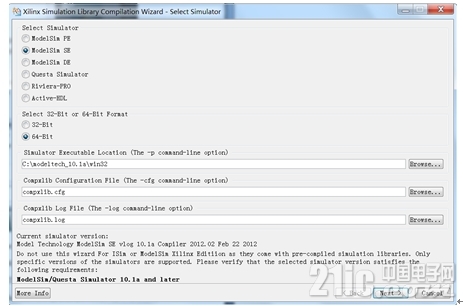

打开工具之后,如图所示,依次做如下设置,一般默认设置即可:● 在“Select Simulator”下面选中你所装好的Modelsim版本,我们这里选择“Modelsim SE”。● 在“Simulator Executable Location”下面填入Modelsim.exe的所在的文件夹,点“Browse…”按钮添加也行,我们的Modelsim SE安装路径是“D:modeltech64_10.1awin32”(不含双引号,下同,除非有特别的说明)。然后点击Next。

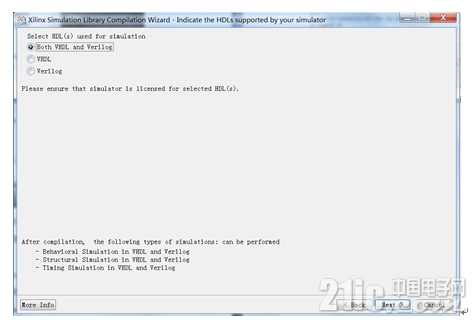

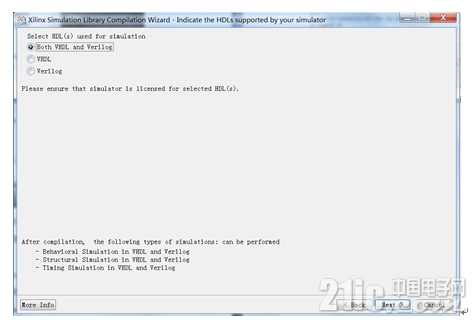

选择需要编译的语言,一般我们使用默认选项“Both VHDL and Verilog”,如图所示,然后点击Next。

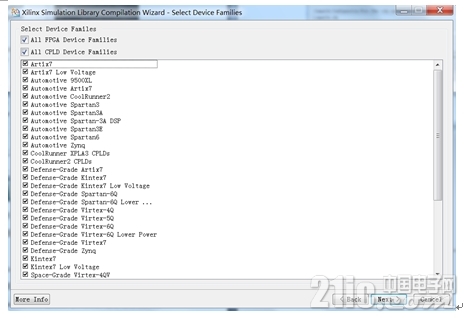

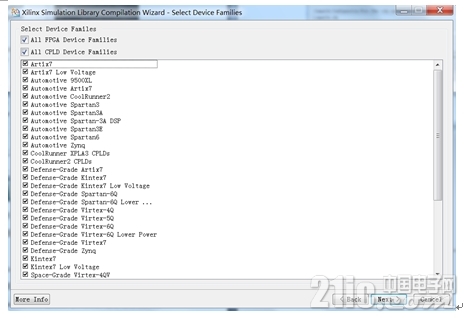

接着如图所示,让我们选择需要编译的Xilinx FPGA和CPLD器件库。这里默认都勾选上。我们也直接点击“Next”继续即可。

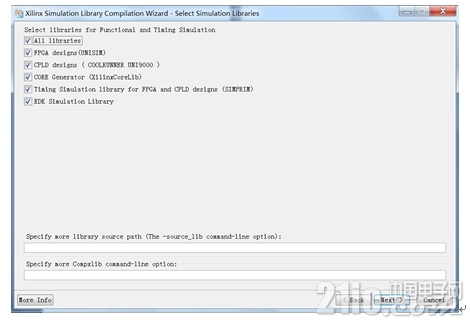

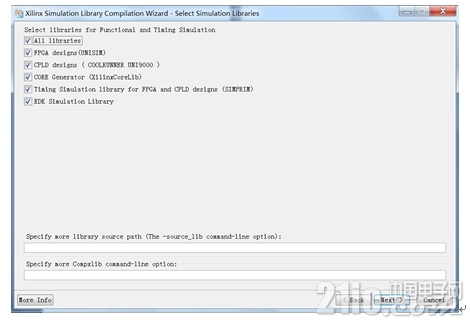

如图所示,这一步默认就行,全选上。下面的两行东东留空即可,那是添加额外库的,第一行是路径,第二行是命令参数,我们用不上就不要填任何东西。点击“Next”。

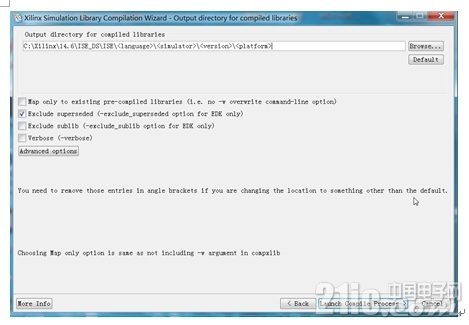

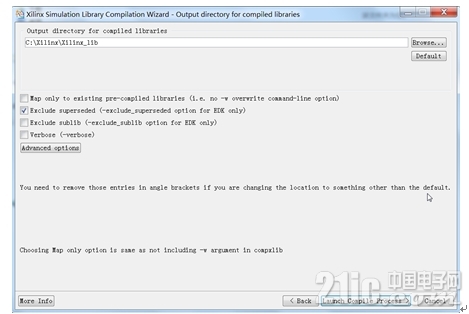

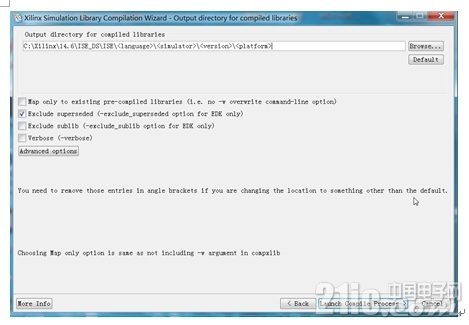

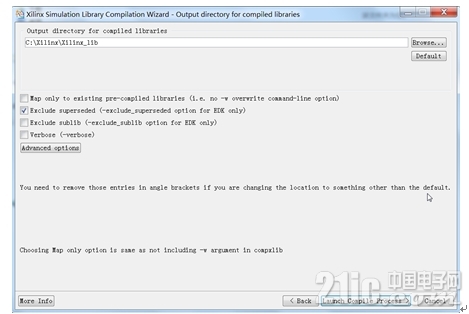

接下来这一步比较重要,在“Output directory for compiled libraries”下面填入输出已编译库的路径,默认也行。个人建议新建一个单独的文件夹,好管理,只要版本一样的,下次直接拿来用,重装也不怕。不过文件夹的名字和整个路径中绝对不能有中文或空格。其他的选项默认便可,之后点“Launch Compiled Process”,如图所示。

此处的设置,以笔者的习惯是先在“C:Xilinx”路径下创建一个名为“Xilinx_lib”的文件夹,如图所示。

接着更改“Output directory for compiled libraries”下的路径为“C:XilinxXilinx_lib”,然后点“LaunchCompiled Process”开始库编译。

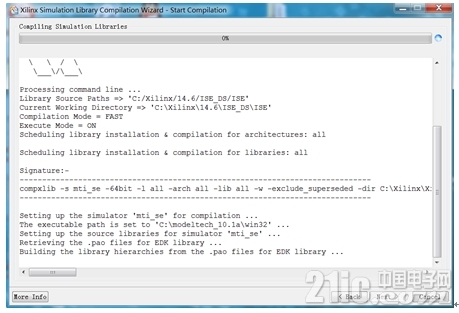

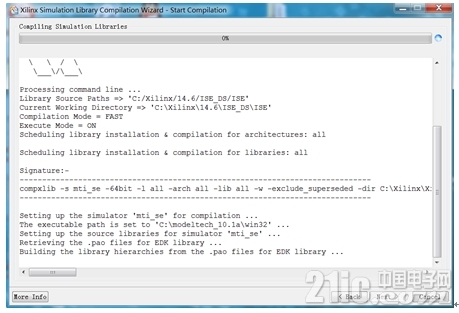

如图所示,开始编译了,整个时间会有一些长(1-2个小时甚至更长,这取决于您的电脑),尤其是有有很长一段时间编译进度会停留在0%,这是正常现象,需要耐心等待。

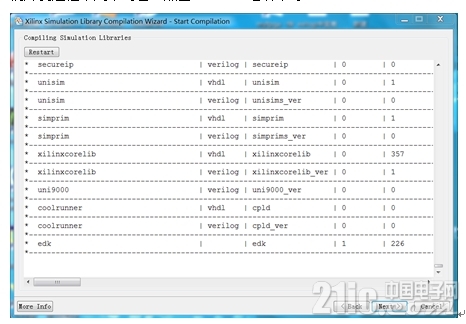

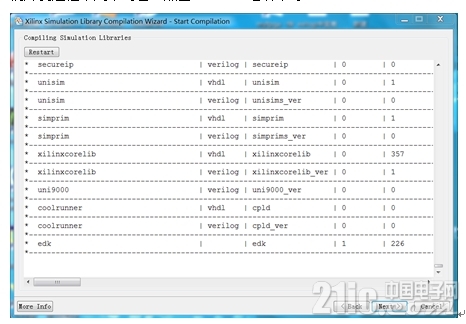

当编译进度到100%后,会跳转到如下图所示的界面,这里报告编译过程中的error和warning,warning可以忽略,error就必须看一下了,若出现了最好回头看看相关路径是否出现了中文或空格、版本是否正确。笔者的编译edk出现了一个error,可以不用理会,我们开发过程中用不到它。点击“Next”继续即可。

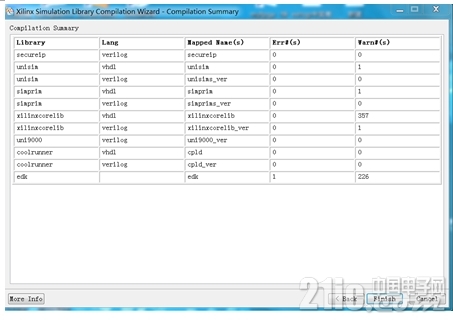

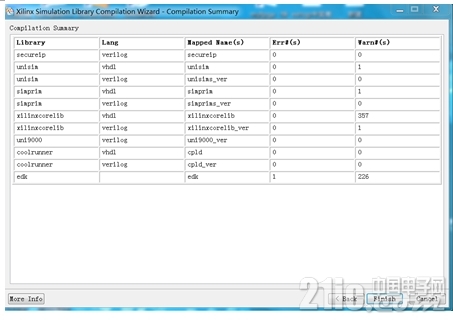

最后一个界面是如图所示的编译报告的summary,点击“Finish”完成整个器件库的编译。

一周热门 更多>