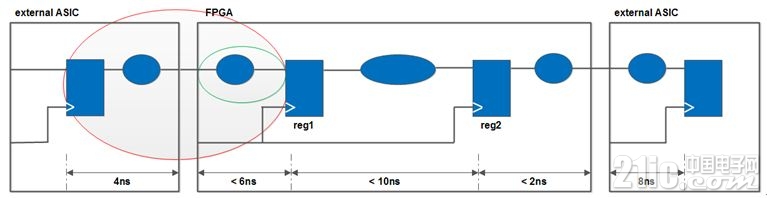

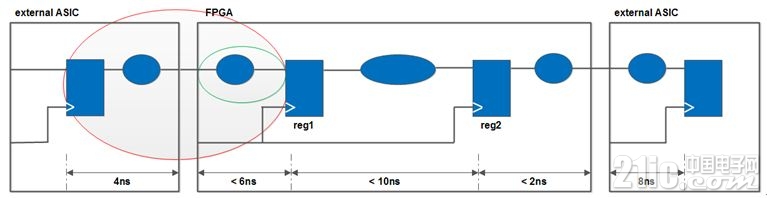

CMOS摄像头接口时序设计1理想时序(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 本实例的CMOS接口是时序分析中典型的pin2reg接口。由于详细的设计说明将在第12章中,因此大家可以先大体浏览过第12章,对整个系统设计有一定了解后,再来进行本节的pin2reg的时序路径分析。(特权同学,版权所有)CMOS Sensor接口相对于FPGA来说是不折不扣的pin2reg所覆盖的约束类型。在开始这个CMOS Sensor的时序约束前,我们先来进一步认识一下pin2reg的约束模型。(特权同学,版权所有)如图8.44所示,前面已经给出的这个模型覆盖了pin2reg、reg2reg和reg2pin这三大类时序路径。本例重点讨论的pin2reg即FPGA和外部芯片连接时,FPGA的输入信号从外部引脚到内部寄存器所经过的延时。图中大圈部分即pin2reg的完整意义上的路径约束起点和终点,而图中小圈部分则是在FPGA内部实际的pin2reg路径,也是我们约束的直接对象。(特权同学,版权所有)在图示中,我们从前面reg2reg分析不难推测,在外部芯片内的源寄存器和在FPGA内部的目的寄存器构成的reg2reg也是需要满足一定的时序要求的,即对应的假设它们有同一个时钟源,是100MHz(对应10ns周期)。那么,如图中假设外部芯片所需要的数据路径延时是4ns,不考虑外部信号和FPGA间的PCB走线延时情况下,FPGA内部的pin2reg路径上的延时就应该是10ns-4ns = 6ns了。时序设计工具一般支持直接约束和间接约束两种方式。所谓直接约束,即设计者自己算出FPGA内部的pin2reg约束是6ns,那么告诉时序设计工具6ns这个数据就OK了;而间接约束,就是设计者告诉时序设计工具FPGA外部的路径上占用了4ns时间,时序设计工具自己有一套运算机制,它也能运算出FPGA内部的pin2reg时间是6ns。而我们这个模型和所使用的约束方式,是间接方式。(特权同学,版权所有)

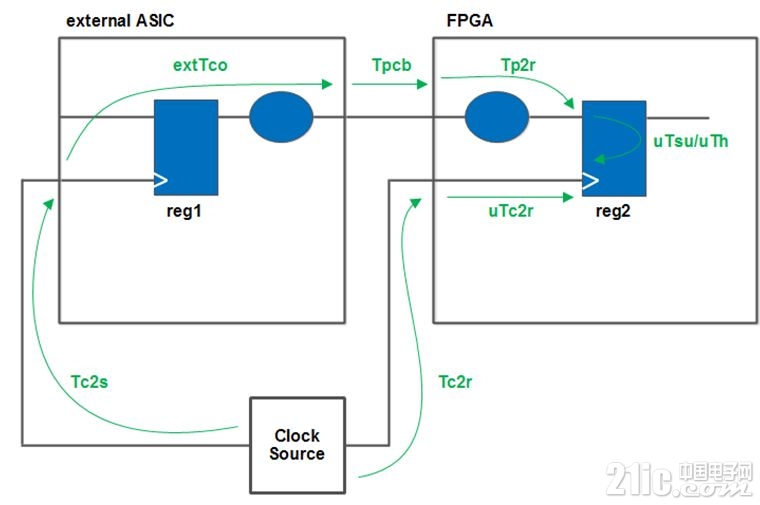

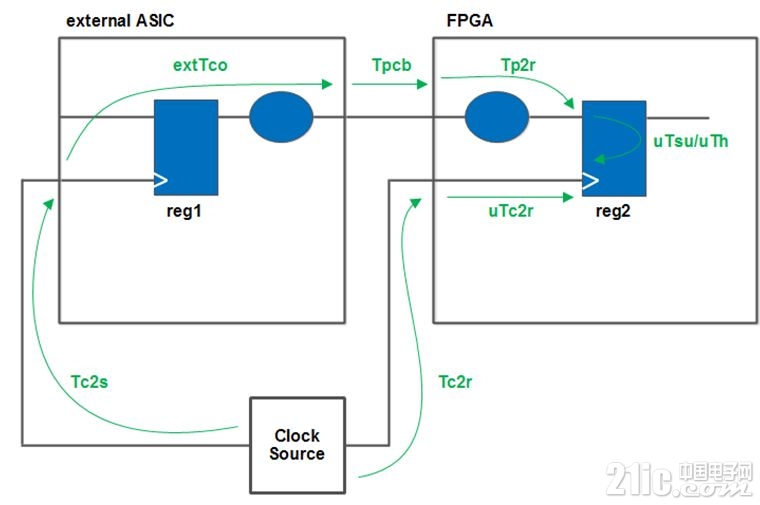

图8.44 pin2reg路径模型如图8.45所示,我们将前面的模型放大。在这个模型中,我们理想的假设外部芯片和FPGA都使用同一个时钟源,这个时钟源到达外部芯片(对应源寄存器)的时钟输入引脚的路径延时(即PCB走线延时)为Tc2s,时钟源到达FPGA的时钟输入引脚的路径延时(即PCB走线延时)为Tc2r。数据信号在外部芯片所经过的总延时值定义为extTco。数据在外部信号和FPGA输入引脚之间所经过的PCB走线延时定义为Tpcb。在FPGA内部,时钟信号的走线延时定义为uTc2r;数据信号的pin2reg延时定义为Tp2r;此外,FPGA内部寄存器的建立时间定义为uTsu,保持时间定义为uTh。(特权同学,版权所有)在这些路径参数中,我们可以简单的分三大类来看。第一类是在PCB上的走线路径,包括Tc2s、Tc2r和Tpcb,这类路径的延时基本上在硬件设计完成后就固定了,而且这些路径的影响通常是微乎其微的(以0.17ns/inch的走线延时计算);第二类是外部芯片中的延时,即extTco,因为外部芯片的时序也都是固定的,我们作为芯片的应用者,无法改变芯片内部时序;第三类是FPGA内部的路径,寄存器固有的uTsu和uTh是随所使用的FPGA器件而定的,通常作为器件的应用者也无法改变,而时钟延时uTc2r虽然是可变的,但是因为FPGA内部一般都有专用的全局时钟网络,专门用于类似时钟信号这样的高扇出、低延时信号,所以uTc2r通常也会控制在一个比较低的范围内,而最有文章可做的就是Tpin2reg的延时值大小了。因此,我们的时序约束关注的重点也就是Tpin2reg延时。(特权同学,版权所有)

图8.45 pin2reg的理想寄存器模型对于以上的路径,参考reg2reg路径的分析,我们不难得到以下的基本建立时间和保持时间要求。(特权同学,版权所有)建立时间需要满足的公式:Launch edge + Tc2s + extTco + Tpcb +Tp2r < latch edge + (Tc2r + uTc2r) - uTsu保持时间需要满足的公式:Launch edge + Tc2s + extTco + Tpcb +Tp2r > latch edge + (Tc2r + uTc2r) + uTh我们可以将以上的两个不等式做些变换,得到如下两个公式。(特权同学,版权所有)建立时间:(Tc2s - Tc2r) + extTco + Tpcb <(latch edge - Launch edge) – uTsu + uTc2r - Tp2r保持时间:(Tc2s - Tc2r) + extTco + Tpcb >(latch edge - Launch edge) + uTh + uTc2r - Tp2r如果取input delay = (Tc2s - Tc2r) + extTco + Tpcb,对照具体的路径,我们不难发现这个input delay实际上就FPGA外部所有延时参数的总和。由此,我们可以得到:input delay < (latch edge - Launchedge) + uTc2r – uTsu - Tp2rinput delay > (latch edge - Launchedge) + uTc2r + uTh - Tp2r我们再来看,Altera官方的handbook中给出了pin2reg路径的建立时间和保持时间的slack计算公式。以下公式中所涉及的input max delay和input min delay也正是我们上面所定义的input delay的最大值和最小值。(特权同学,版权所有)建立时间余量计算公式:Setup time slack = Data Required Time–Data Arrival TimeData Arrival Time = Launch Edge +input max delay + Tp2rData Required Time = Latch Edge +uTc2r – uTsu保持时间余量计算公式:Hold time slack = Data Arrival Time –Data Required TimeData Arrival Time = Launch Edge +input min delay + Tp2rData Required Time = Latch Edge +uTc2r + uTh

一周热门 更多>