VGA驱动接口时序设计之3时钟约束本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 如图8.26所示,FPGA产生的数据data_out和时钟clk_out的理想波形是时钟上升沿锁存到稳定可靠的数据。(特权同学,版权所有)

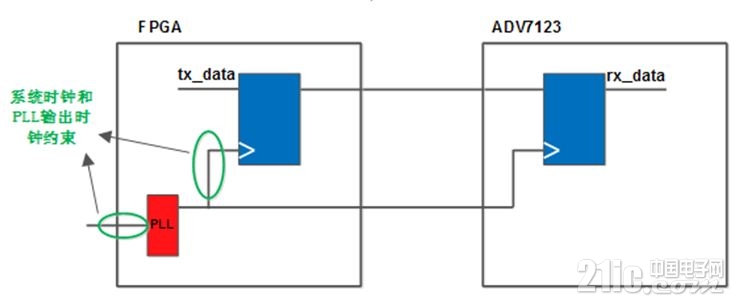

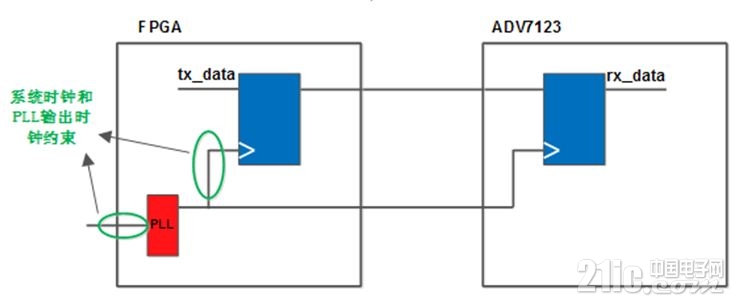

图8.26 源同步接口寄存器和时序波形关系下面我们来探讨如何对这个设计进行约束。首先,对系统的输入时钟(25MHz)、PLL产生的时钟进行约束。约束脚本如下。(特权同学,版权所有)create_clock -name {clk} -period 40.000 -waveform { 0.000 20.000} [get_ports {clk}] derive_pll_clocks –use_tan_namederive_pll_clocks语句将会自动且准确覆盖PLL产生的所有时钟路径。在本实例中,以上的约束将会覆盖如图8.27所示的时钟。(特权同学,版权所有)

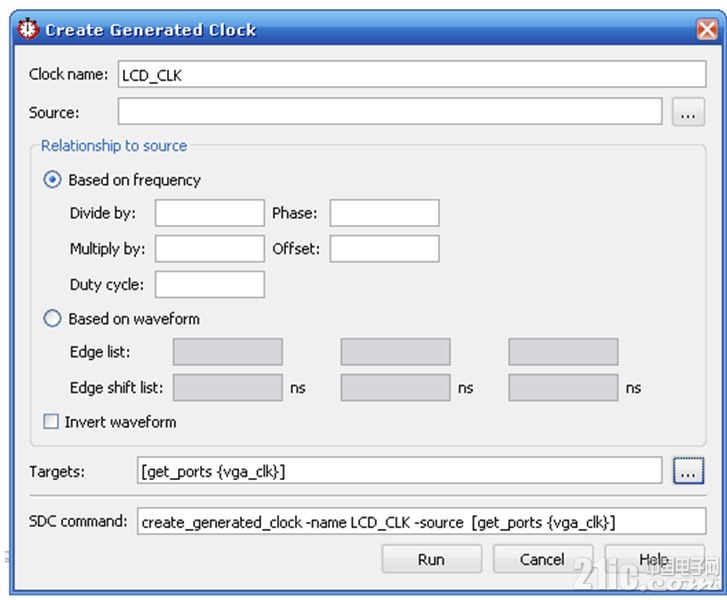

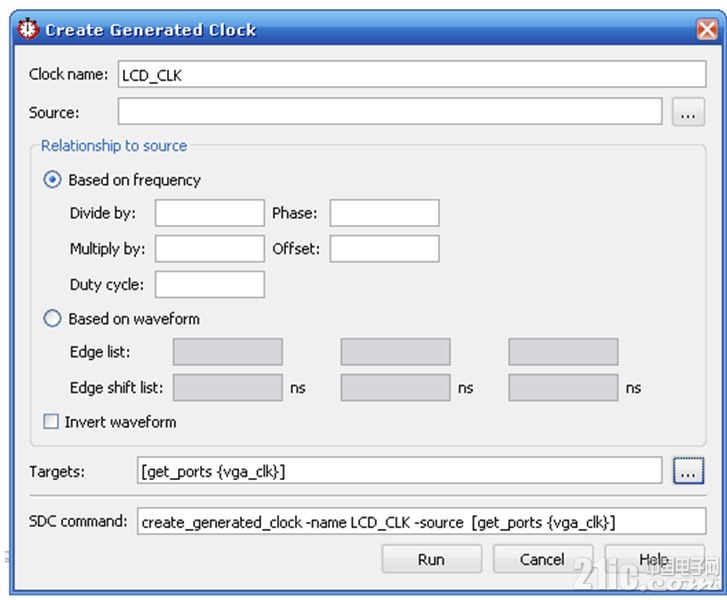

图8.27 时钟约束可覆盖路径接着,对lcd_clk这个时钟进行约束,它需要约束为虚拟(virtul)时钟,将会被用于output port上的数据锁存时钟。因为我们这个工程可能会用到25MHz的lcd_clk,也会用到50MHz的lcd_clk,因此我们以频率更高的50MHz为例进行说明。系统的50MHz是PLL的clk[1]输出的,因此我们约束这个虚拟时钟如图8.28所示。(特权同学,版权所有)

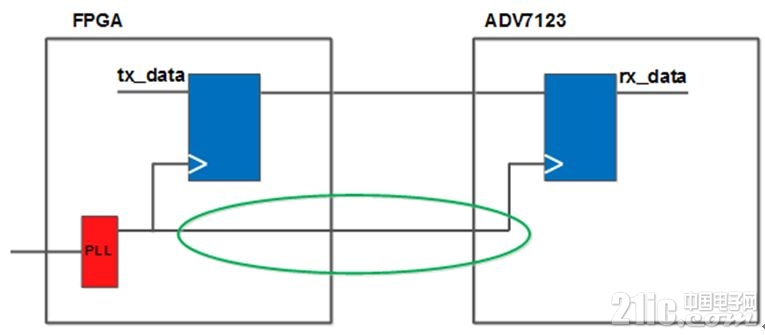

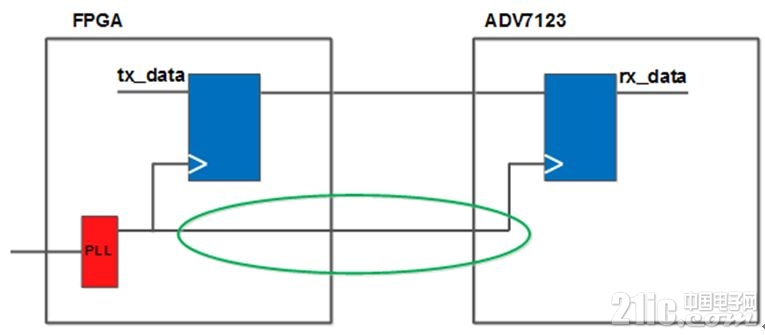

图8.28 虚拟时钟约束对应的脚本如下。(特权同学,版权所有)create_generated_clock -name LCD_CLK -source [get_ports {vga_clk}]这个虚拟时钟将会在FPGA内部对tx_data的reg2pin进行时序分析时作为latch时钟。实际对于一般的reg2reg路径的分析,由于他们的launch和latch时钟都在FPGA内部,若像前面一样做过时钟的约束,那么FPGA对这些内部的时钟就已心知肚明,无需什么虚拟时钟。而对于pin2reg或reg2pin的路径分析,则一般都需要用户指定一个符合相关时钟要求的虚拟时钟,这个虚拟时钟就作为pin端的时钟来分析时序,我们这里所约束的虚拟时钟对应的路径如图8.29所示。(特权同学,版权所有)

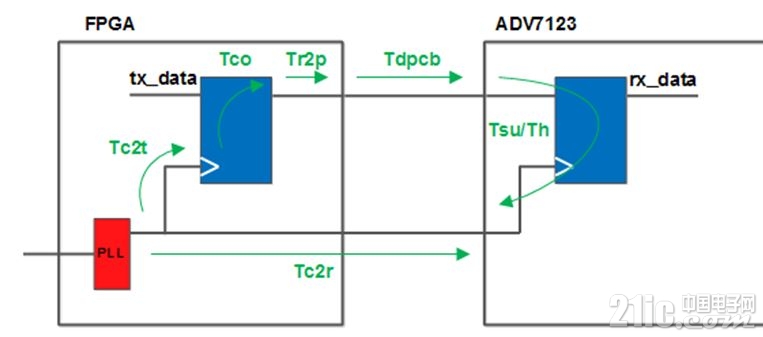

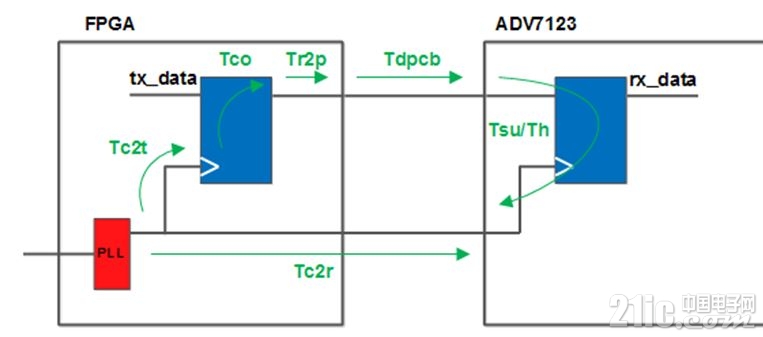

图8.29 虚拟时钟路径如图8.30所示,有了时钟lcd_clk,我们才能对数据路径进行合适的约束。本例中,有两条关于时钟的路径延时,我们假设PLL输出的时钟是源和目的时钟的起点,以这个点为基准,时钟到达源寄存器,其路径延时为Tc2t;时钟到达目的寄存器,即ADV7123芯片的引脚输入端,其路径延时为Tc2r,这个延时包括了时钟从PLL输出到FPGA引脚的延时以及时钟从FPGA的引脚到ADV7123引脚的延时,后者的延时是PCB走线产生的延时。再来看数据路径,数据首先进入源寄存器的输入端口后,在源寄存器内部经过延时Tco,接着数据从源寄存器的输出端口到FPGA引脚上的延时Tr2p,还有就是数据在PCB上的延时Tdpcb,最后在计算ADV7123的时序时,我们必须将数据的建立时间Tsu和保持时间Th考虑在内。(特权同学,版权所有)

图8.30 时序路径模型

一周热门 更多>