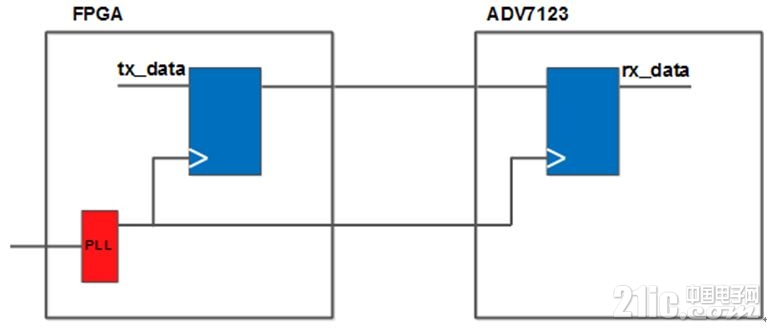

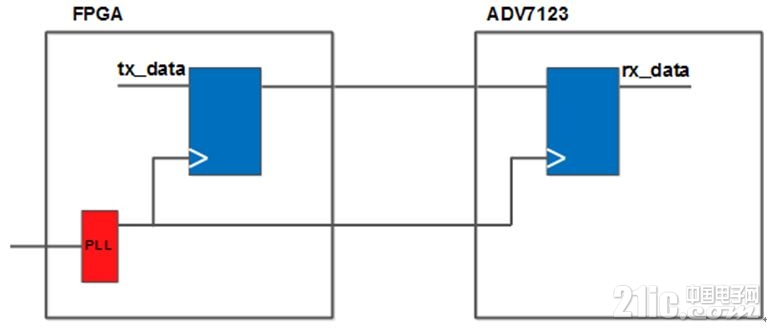

VGA驱动接口时序设计之2源同步接口本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 好,有了这些信息,我们可以分析一下这个接口的时序要求,然后对其进行约束。这个输出的信号,其实是很典型的源同步接口,它的时钟和数据都是由FPGA来驱动产生的。一般的源同步接口的寄存器模型如图8.25所示。在我们的这个系统中,发送端是FPGA,而接收端是ADV7123芯片。如果传输的速率比较高,那么数据和时钟上升沿的严格对齐则要依靠PLL产生可调相位的时钟信号来保证。不过,我们这个25MHz或者50MHz的时钟通过较好的时序分析和约束后,则不必动用PLL。(特权同学,版权所有)

图8.25 源同步接口寄存器模型

一周热门 更多>