本帖最后由 pszcmzcm 于 2015-6-29 12:40 编辑

新人求助schematic 综合的一点问题

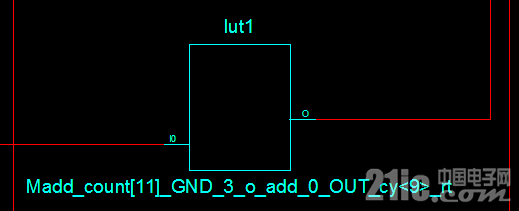

在综合后 technology schematic中 有数个LUT(如图所示)感觉没有意义属于资源浪费

EDA为ISE14.7

truetable为

input output

0 0

1 1

考虑了一下应该是VHDL编写上的问题,大学中虽然涉及了FPGA 也 在Tutorial 中 学了基本的VHDL编写,但对于此类问题还是感觉无从下手,现在自学并为Msc准备中,希望大牛能告知一下解决方法和原理

code为简单的双向交通灯(FSM based)

具体如下:

新人求助schematic 综合的一点问题

在综合后 technology schematic中 有数个LUT(如图所示)感觉没有意义属于资源浪费

EDA为ISE14.7

truetable为

input output

0 0

1 1

考虑了一下应该是VHDL编写上的问题,大学中虽然涉及了FPGA 也 在Tutorial 中 学了基本的VHDL编写,但对于此类问题还是感觉无从下手,现在自学并为Msc准备中,希望大牛能告知一下解决方法和原理

code为简单的双向交通灯(FSM based)

具体如下:

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- entity Traffic_light is

- port(clk:in std_logic;

- Test: in std_logic;

- Standby:in std_logic;

- R1,Y1,G1:out std_logic;

- R2,Y2,G2:out std_logic);

-

- end Traffic_light;

- architecture Behavioral of Traffic_light is

- constant time_max :integer := 2700;

- --The frequency of Clk is 60Hz--

- constant time_RG :integer := 1800;

- --time of light change from red & green(s)--

- constant time_RY :integer := 300;

- --time of light change from red & yellow(s)--

- constant time_GR :integer := 2700;

- --time of light change from green & red(s)--

- constant time_YR :integer := 300;

- --time of light change from yellow & red(s)--

- constant time_test :integer := 60;

- --time for test mode(s)--

- type state is (state_RY,state_GR,state_YR,state_RG,state_YY);

- signal Pr_state,Nx_state: state;

- signal time: integer range 0 to time_max;

- begin

- --lower section of state machine--

- process(clk,standby)

- variable count: integer range 0 to time_max;

- begin

- if (standby = '1') then

- Pr_state <= state_yy;

- elsif (clk'event and clk= '1') then

- count := count +1;

- if (count = time ) then

- Pr_state <= Nx_state;

- count := 0;

- end if;

- end if;

- end process;

- --upper section of state machine--

- process(pr_state,test)

- begin

- case pr_state is

- --state_RY--

- when state_RY =>

- R1 <= '1'; G1 <= '0'; Y1 <= '0';

- R2 <= '0'; G2 <= '0'; Y2 <= '1';

- Nx_state <= state_GR;

- if (test = '0') then time <= time_RY;

- else time <= time_test;

- end if;

- --state_GR--

- when state_GR =>

- R1 <= '0'; G1 <= '1'; Y1 <= '0';

- R2 <= '1'; G2 <= '0'; Y2 <= '0';

- Nx_state <= state_YR;

- if (test = '0') then time <= time_GR;

- else time <= time_test;

- end if;

- --state_YR--

- when state_YR =>

- R1 <= '0'; G1 <= '0'; Y1 <= '1';

- R2 <= '1'; G2 <= '0'; Y2 <= '0';

- Nx_state <= state_RG;

- if (test = '0') then time <= time_YR;

- else time <= time_test;

- end if;

- --state_RG--

- when state_RG =>

- R1 <= '1'; G1 <= '0'; Y1 <= '0';

- R2 <= '0'; G2 <= '1'; Y2 <= '0';

- Nx_state <= state_RY;

- if (test = '0') then time <= time_RG;

- else time <= time_test;

- end if;

- when others =>

- R1 <= '0'; G1 <= '0'; Y1 <= '1';

- R2 <= '0'; G2 <= '0'; Y2 <= '1';

- Nx_state <= state_RY;

- end case;

- end process;

- end Behavioral;

一周热门 更多>