FPGA核心板电路设计架构本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

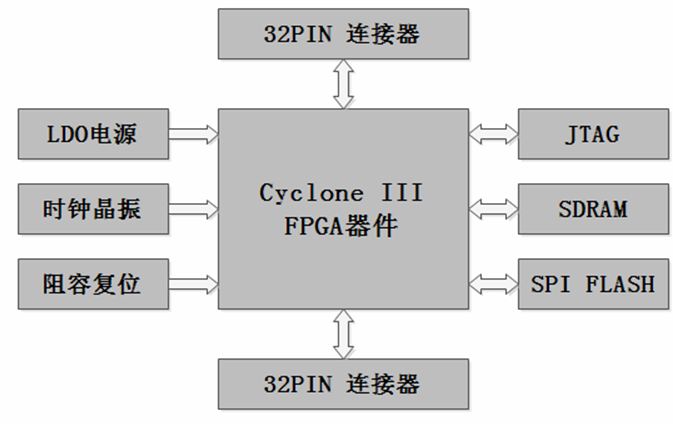

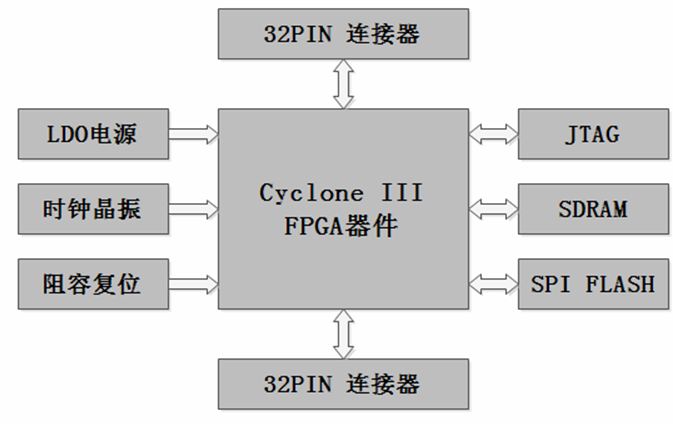

核心板除了一颗昂贵的CycloneIII系列FPGA芯片外,电源、复位、时钟、JTAG一个不能少。我们这可颗芯片的电源有三档,即3.3V、2.5V和1.2V。3.3V是供给FPGA的I/O电压,也是系统的其他外设芯片(如SDR SDRAM和SPI FLASH)的电源电压;2.5V是供给JTAG电路和FPGA的PLL电源所需要的;1.2V则是FPGA的内核电压。使用的时钟是25MHz,有人说这么低,不够用的?非也,FPGA内部的PLL就是专门负责管理时钟的,它可以对外部输入的25MHz时钟进行倍频或分频,甚至非整数倍的倍频或分频也能够办到。JTAG是用于PC和FPGA连接的电路,PC上的Quartus II下载烧录就是通过这个接口。核心板电路架构框图如图3.10所示。(特权同学,版权所有)

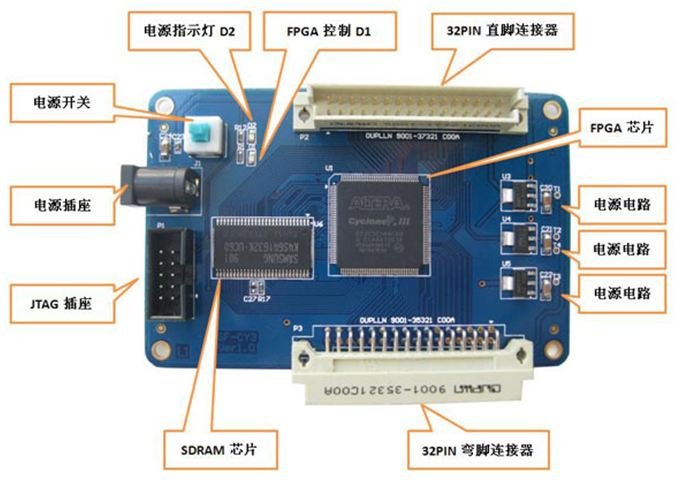

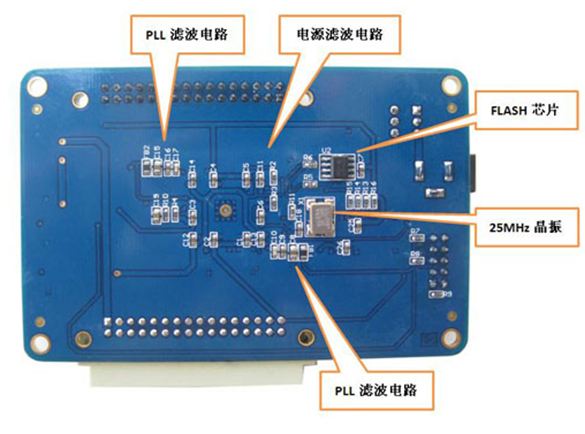

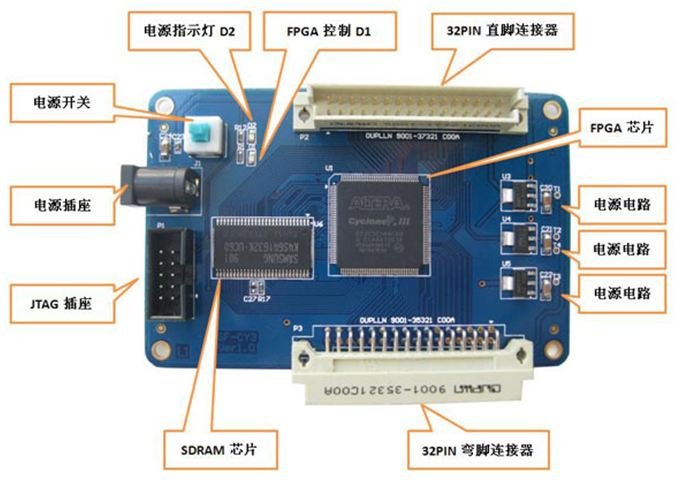

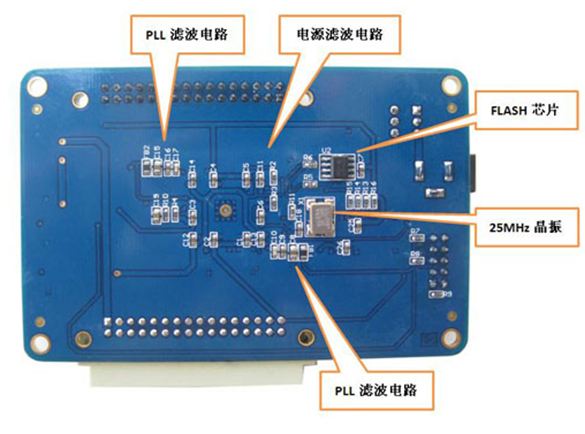

图3.10 核心板电路架构框图另外,有两颗存储器,SPIFLASH用于FPGA器件的上电配置数据存储,我们都知道FPGA是基于RAM结构的,下电后不能够保存数据,所以需要一颗非易失的FLASH用于存储FPGA的配置数据。当FPGA上电后,它本身没有可立即执行的应用数据,但是通过专有的SPI接口连接到SPI FLASH将数据搬运到RAM上后,FPGA就能够运行起来了。SDR SDRAM是用于做扩展使用的,它既可以作为NIOS II处理器的RAM运行程序,也可以作为后续LCD等需要实时大数据量存储的缓存应用。另外,上下两个32PIN的连接器,分别引出23个I/O引脚,各种扩展板卡就通过他们做文章了。(特权同学,版权所有)如图3.11和图3.12所示,我们可以先来认识一下核心电路板的各个重要元器件。(特权同学,版权所有)

图3.11 核心电路板正面视图

图3.12 核心电路板背面视图

核心板除了一颗昂贵的CycloneIII系列FPGA芯片外,电源、复位、时钟、JTAG一个不能少。我们这可颗芯片的电源有三档,即3.3V、2.5V和1.2V。3.3V是供给FPGA的I/O电压,也是系统的其他外设芯片(如SDR SDRAM和SPI FLASH)的电源电压;2.5V是供给JTAG电路和FPGA的PLL电源所需要的;1.2V则是FPGA的内核电压。使用的时钟是25MHz,有人说这么低,不够用的?非也,FPGA内部的PLL就是专门负责管理时钟的,它可以对外部输入的25MHz时钟进行倍频或分频,甚至非整数倍的倍频或分频也能够办到。JTAG是用于PC和FPGA连接的电路,PC上的Quartus II下载烧录就是通过这个接口。核心板电路架构框图如图3.10所示。(特权同学,版权所有)

一周热门 更多>