本帖最后由 ysdx 于 2014-12-3 14:40 编辑

以前用CYCLONE IV连接DDRII的时候,布线时没有使用电阻上拉到VTT,也没有串电阻.就是直接连接的.跑着没有什么问题.现在想用strayix ii连接DDRII.由于这次是硬核的,频率快些.是否需要连接呢?有谁有实际经验啊?能不能省?如果能够省,布线容易多了.

另:

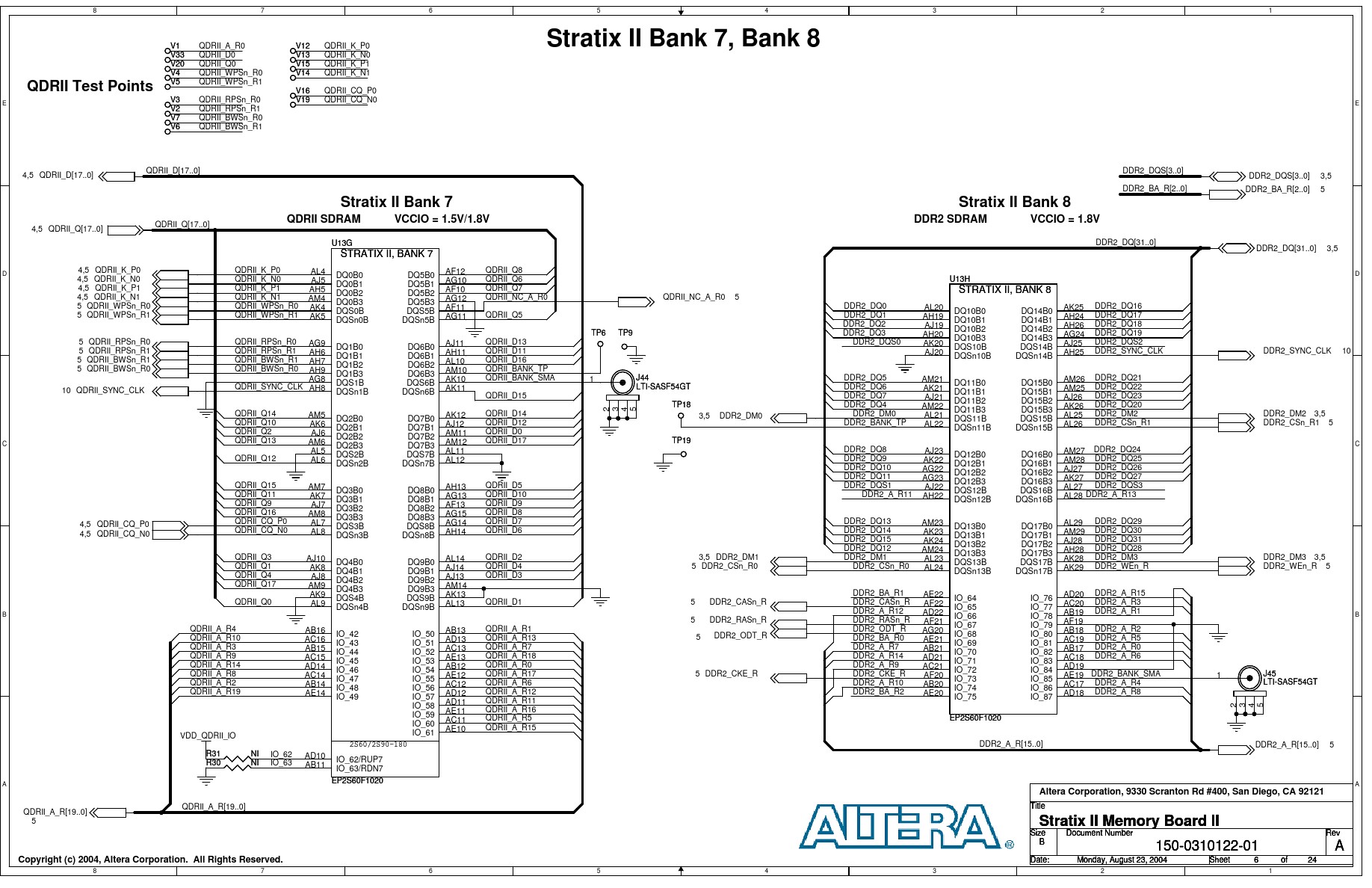

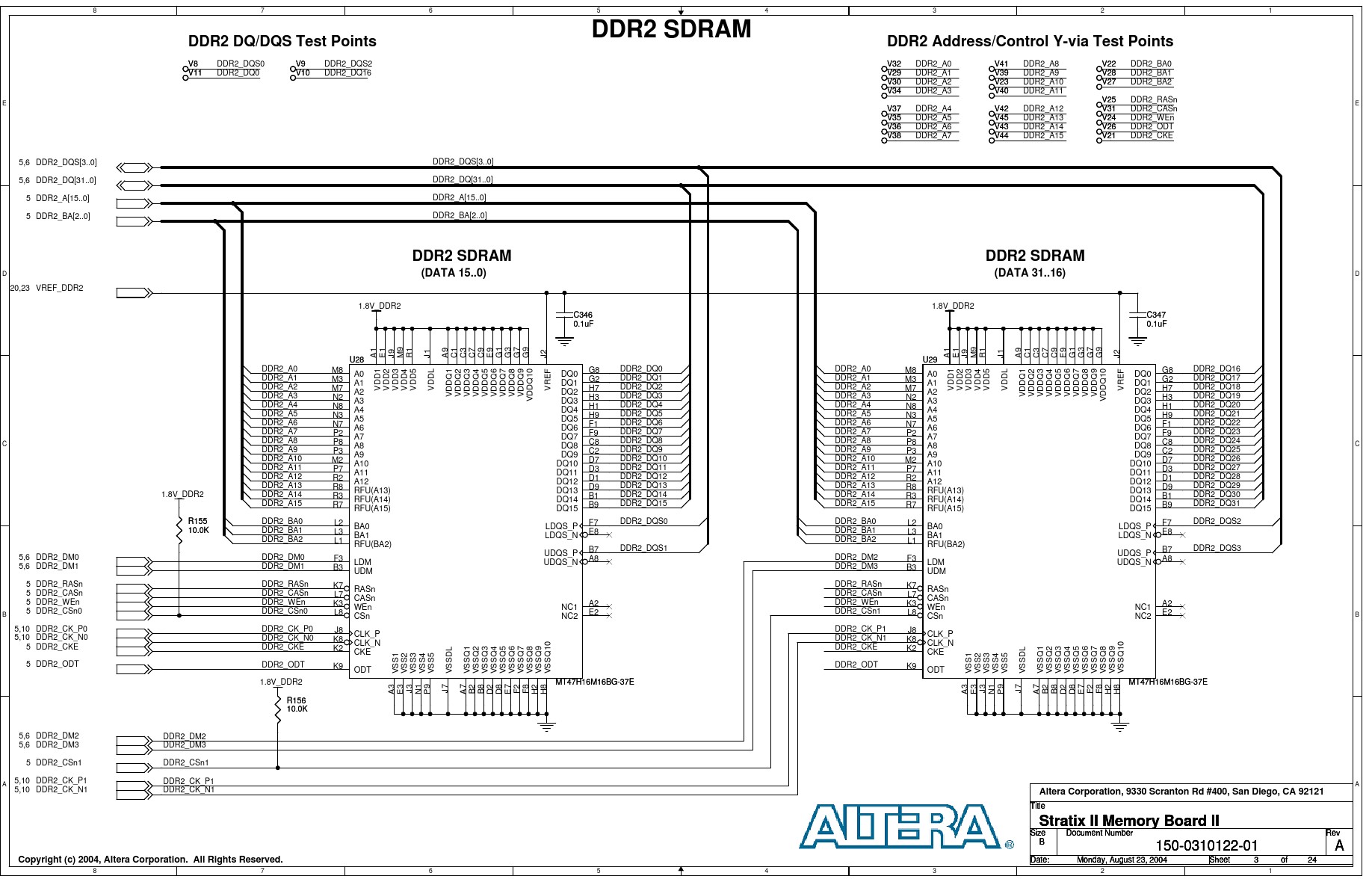

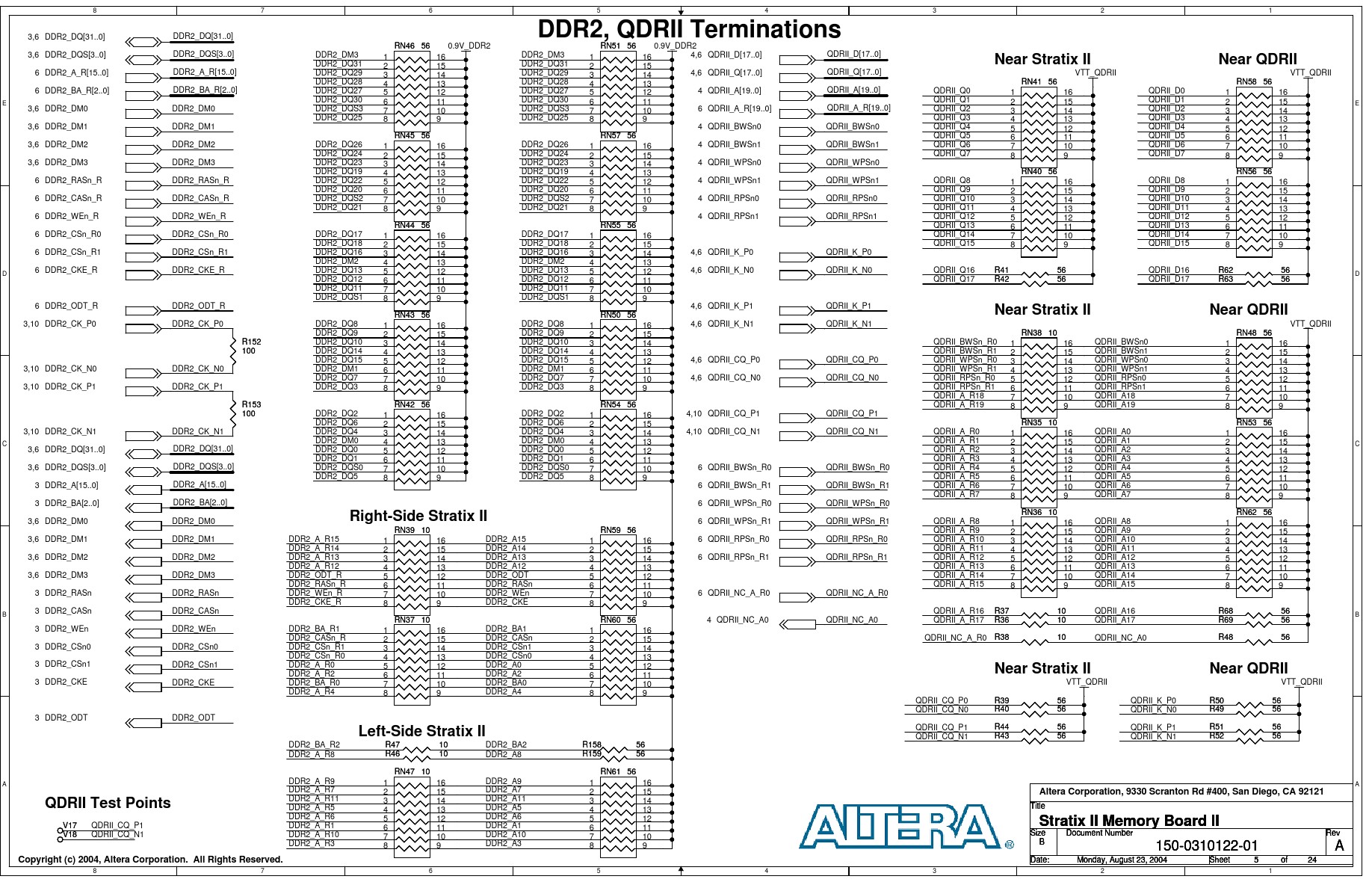

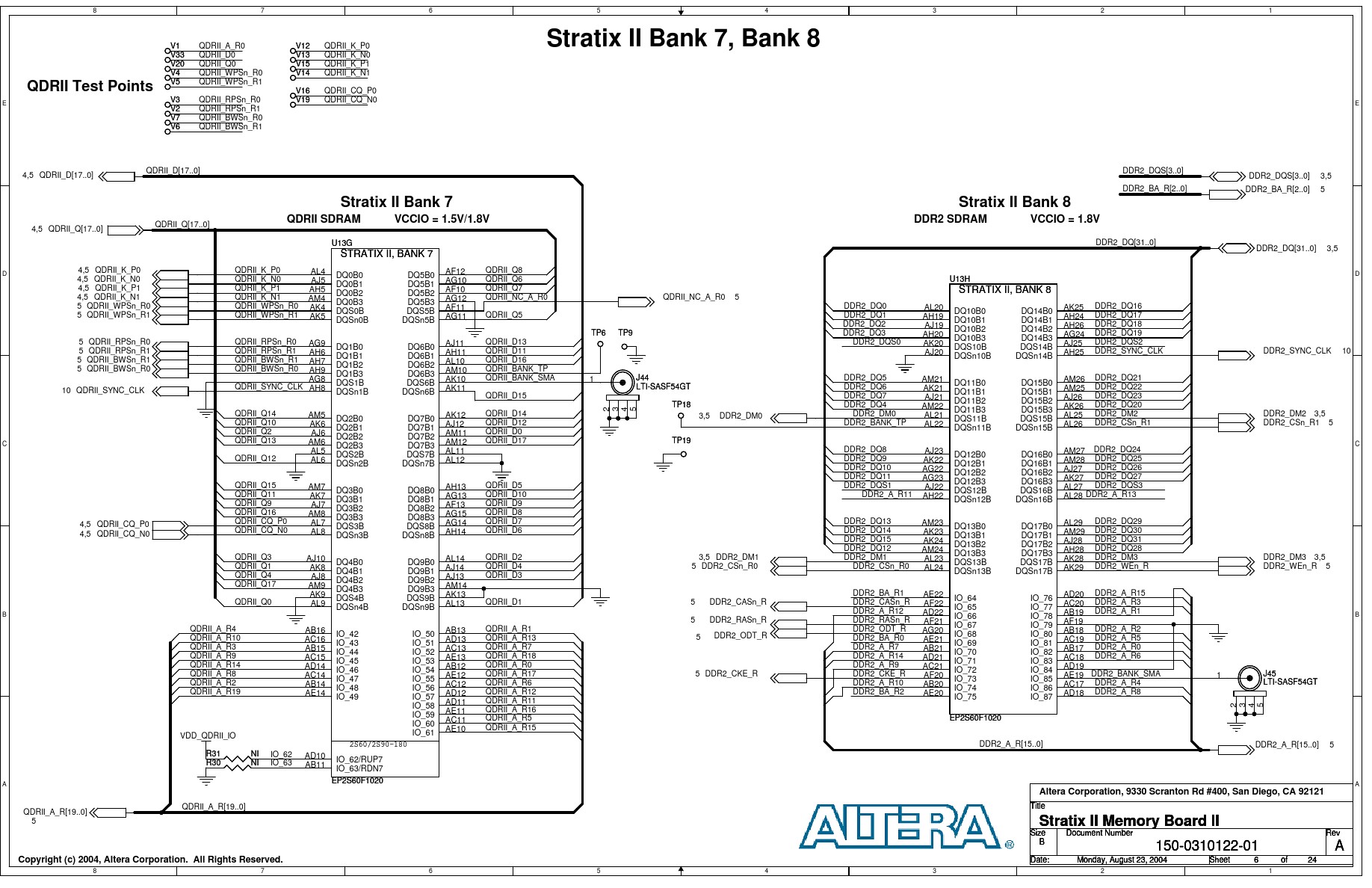

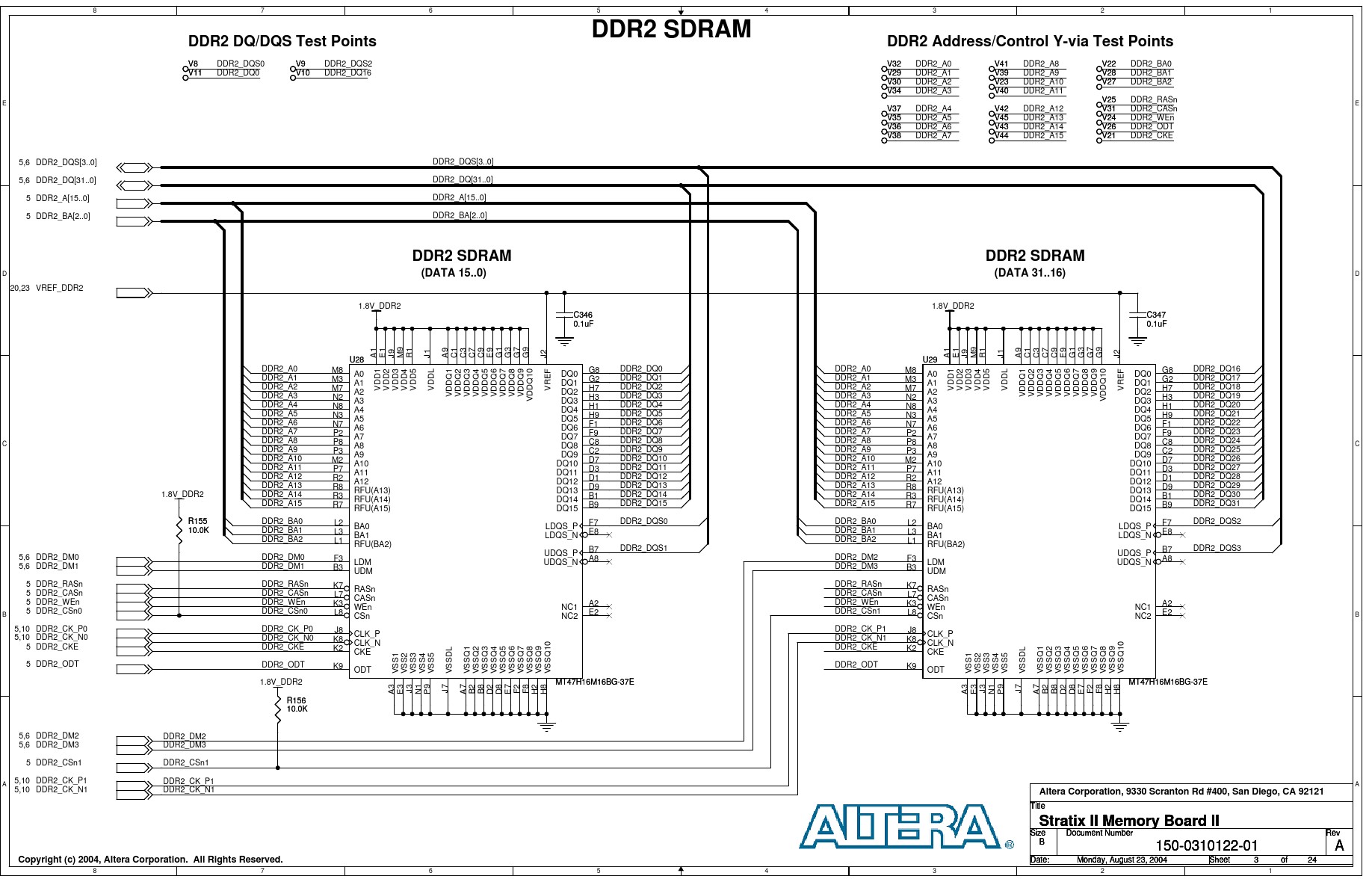

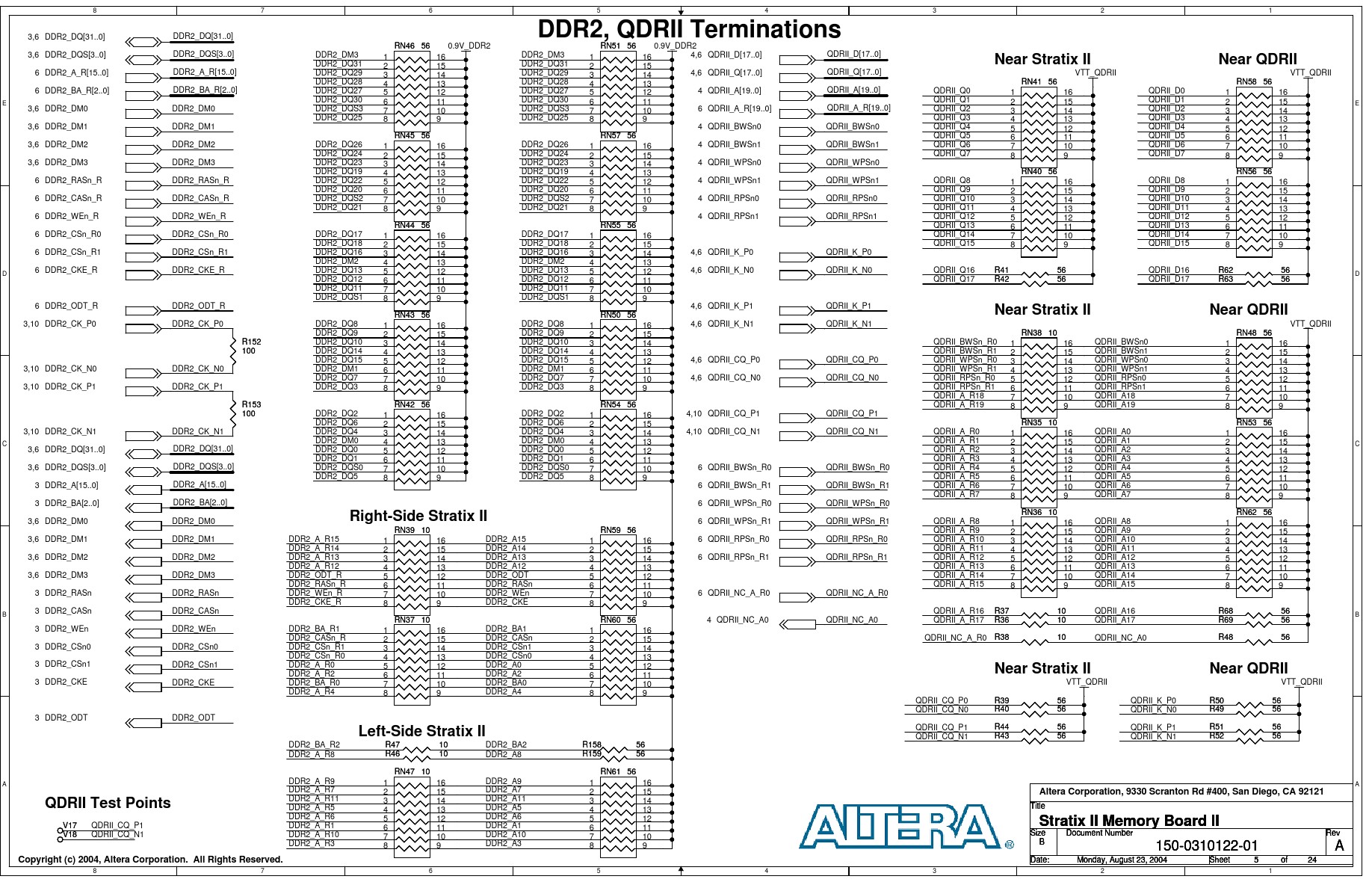

我看了"基于StratixII的DDR2,QDR2和SRAM的原理图和评估板"的原理图,确实是加了的.不但加了,地址控制线上还串了10欧电阻,这玩意导致布线更麻烦了.还有一点不明白的是,图中数据线怎么用两组上拉啊????我感觉数据线上应该能够不加电阻,毕竟DDRII 的ODT控制连接到FPGA了.地址线上串电阻也不必,上拉倒是可以加上.一般这种外挂的DDRII和FPGA距离都很短.

以前用CYCLONE IV连接DDRII的时候,布线时没有使用电阻上拉到VTT,也没有串电阻.就是直接连接的.跑着没有什么问题.现在想用strayix ii连接DDRII.由于这次是硬核的,频率快些.是否需要连接呢?有谁有实际经验啊?能不能省?如果能够省,布线容易多了.

另:

我看了"基于StratixII的DDR2,QDR2和SRAM的原理图和评估板"的原理图,确实是加了的.不但加了,地址控制线上还串了10欧电阻,这玩意导致布线更麻烦了.还有一点不明白的是,图中数据线怎么用两组上拉啊????我感觉数据线上应该能够不加电阻,毕竟DDRII 的ODT控制连接到FPGA了.地址线上串电阻也不必,上拉倒是可以加上.一般这种外挂的DDRII和FPGA距离都很短.

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>