本帖最后由 tangjianyuan 于 2015-3-6 13:08 编辑

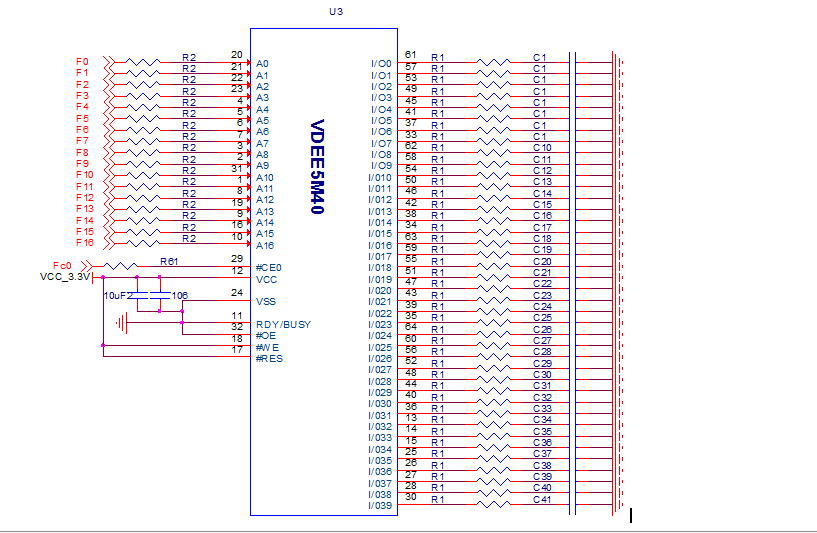

大家好,请问一下FPGA的大神们,想问一下大家这个多频率怎么编写啊,这是一款EEPROM存储芯片,要求输入如下面频率信号。图中电源电压VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1×(1±10%)KΩ,C1 = 30×(1±10%)pF。输入信号F0 = 1MHz,F1 = F0/2,F2 = F1/2,F3 = F2/2,F4 = F3/2,F5 = F4/2,F6 = F5/2,F7 = F6/2,F8 = F7/2,F9 = F8/2,F10 = F9/2,F11 = F10/2,F12 = F11/2,F13 = F12/2,F14 = F13/2,F15 = F14/2,F16 = F15/2,FC0 = 500KHZ。对于这个F0,F1,F2,F3,F4,F5,,,怎么样进行处理。

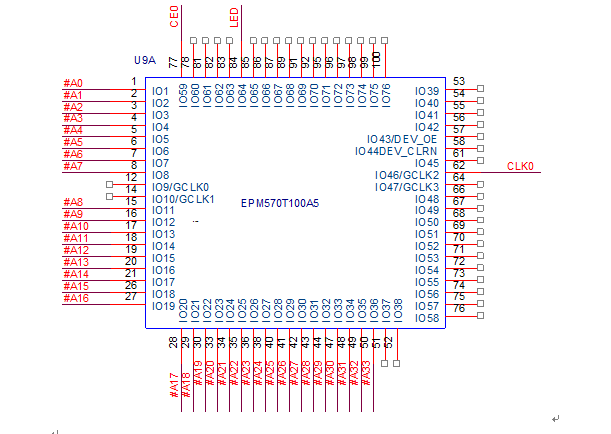

时钟频率由外部clk0产生50MHZ的晶振,从CLK0输入到CPLD芯片内部,但现在我有点不知道怎么把50HMZ的频率,每次都二分频,给到不同的地址上去,百度过,想到用二分频的方法,由于小弟对FPGA不很会用,只是在学校学习过VHDL语言,有些语法还不太会用。请大神们指点一下。下面是我预先写的一个程序,在处理地址上的不同频率还不太对。望指点一下感激不尽。

module VDEE5M40VS(clk_in,cs,led,rest,address);

input clk_in,rest;output [2:0] led;output [16:0] address;output cs;

reg cs;reg clk_out;reg clk_500k;reg [2:0] led;reg [49:0] j; // 1MHZ counter datareg [99:0] k; // 500khz counter datareg [31:0] count1;reg [31:0] num;reg [16:0] address;reg [35:0] count2;parameter N=36;

initial begin count1 <=32'h0000_0000; count2<=32'h0000_0000; num<= 32'h0000_0000; led<= 3'hf0; cs<=1'b0; address<= 17'h0000_0000;end

always @(posedge clk_in)begin if(count2==N/2-1) // 50MHZfrequency counter number 50 generate 1MHZ begin clk_out <=!clk_out; count2 <=0; end else count2<= count2+1'b1;

end/******************************************************************* LED Control 1s 闪烁********************************************************************/

always @(posedge clk_in) begin if(num == 32'd50000000) begin led[0]<=~led[0]; num<=32'b0; end else begin num <= num +1'b1; endend/******************************************************************** address control 这里F0,F1,F2,F3,,,,的多频率/2,加载到不同的地址线上,不知改如何处理**********************************************************************/ always@(posedge clk_out) begin if(count1 <= 32'd50) begin if(count1 %2 ==1'b1) begin //we <= 1'b1; //oe <= 1'b1; address <= address+1'b1; end elsebegin //we <= 1'b1; // oe <= 1'b1; address <= address; end count1 <=count1+1'b1; end elsebegin led [2] <= ~led [2]; count1<= 32'h0000000; address<=17'h000000;

end end/******************************************************************** generate 500kHZ frequency**********************************************************************/always @(posedge clk_in) //50MHZ clk 时钟信号产生 500KHZ信号begin if(k==100) //500KHZ=50MHZ/100 begin k <=0; clk_500k <=~clk_500k; end

end/******************************************************************** chip cs0 control**********************************************************************/ always @(posedge clk_500k)begin if(led[2] <=1'b0) begin cs<= ~cs; end else cs<= 1'b1;

endendmodule

大家好,请问一下FPGA的大神们,想问一下大家这个多频率怎么编写啊,这是一款EEPROM存储芯片,要求输入如下面频率信号。图中电源电压VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1×(1±10%)KΩ,C1 = 30×(1±10%)pF。输入信号F0 = 1MHz,F1 = F0/2,F2 = F1/2,F3 = F2/2,F4 = F3/2,F5 = F4/2,F6 = F5/2,F7 = F6/2,F8 = F7/2,F9 = F8/2,F10 = F9/2,F11 = F10/2,F12 = F11/2,F13 = F12/2,F14 = F13/2,F15 = F14/2,F16 = F15/2,FC0 = 500KHZ。对于这个F0,F1,F2,F3,F4,F5,,,怎么样进行处理。

时钟频率由外部clk0产生50MHZ的晶振,从CLK0输入到CPLD芯片内部,但现在我有点不知道怎么把50HMZ的频率,每次都二分频,给到不同的地址上去,百度过,想到用二分频的方法,由于小弟对FPGA不很会用,只是在学校学习过VHDL语言,有些语法还不太会用。请大神们指点一下。下面是我预先写的一个程序,在处理地址上的不同频率还不太对。望指点一下感激不尽。

module VDEE5M40VS(clk_in,cs,led,rest,address);

input clk_in,rest;output [2:0] led;output [16:0] address;output cs;

reg cs;reg clk_out;reg clk_500k;reg [2:0] led;reg [49:0] j; // 1MHZ counter datareg [99:0] k; // 500khz counter datareg [31:0] count1;reg [31:0] num;reg [16:0] address;reg [35:0] count2;parameter N=36;

initial begin count1 <=32'h0000_0000; count2<=32'h0000_0000; num<= 32'h0000_0000; led<= 3'hf0; cs<=1'b0; address<= 17'h0000_0000;end

always @(posedge clk_in)begin if(count2==N/2-1) // 50MHZfrequency counter number 50 generate 1MHZ begin clk_out <=!clk_out; count2 <=0; end else count2<= count2+1'b1;

end/******************************************************************* LED Control 1s 闪烁********************************************************************/

always @(posedge clk_in) begin if(num == 32'd50000000) begin led[0]<=~led[0]; num<=32'b0; end else begin num <= num +1'b1; endend/******************************************************************** address control 这里F0,F1,F2,F3,,,,的多频率/2,加载到不同的地址线上,不知改如何处理**********************************************************************/ always@(posedge clk_out) begin if(count1 <= 32'd50) begin if(count1 %2 ==1'b1) begin //we <= 1'b1; //oe <= 1'b1; address <= address+1'b1; end elsebegin //we <= 1'b1; // oe <= 1'b1; address <= address; end count1 <=count1+1'b1; end elsebegin led [2] <= ~led [2]; count1<= 32'h0000000; address<=17'h000000;

end end/******************************************************************** generate 500kHZ frequency**********************************************************************/always @(posedge clk_in) //50MHZ clk 时钟信号产生 500KHZ信号begin if(k==100) //500KHZ=50MHZ/100 begin k <=0; clk_500k <=~clk_500k; end

end/******************************************************************** chip cs0 control**********************************************************************/ always @(posedge clk_500k)begin if(led[2] <=1'b0) begin cs<= ~cs; end else cs<= 1'b1;

endendmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

initial你说的没错,它只能用于仿真,这应该不影响结果输出吧,我把它屏蔽了,我寄存器的值也不能从DIV_CLK 输出

一周热门 更多>