本帖最后由 sunnyqd 于 2014-8-26 11:47 编辑

Copy of k3.jpg (34.93 KB, 下载次数: 0)

下载附件

2014-8-26 11:18 上传

Copy of k3.jpg (34.93 KB, 下载次数: 0)

下载附件

2014-8-26 11:18 上传

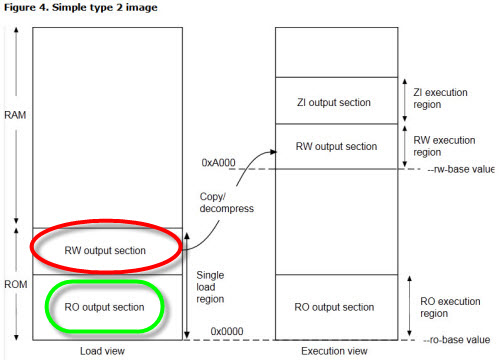

Region Table即位图中红 {MOD}圈圈内的的一部分,另一部分是压缩后的数据,由Region Table指向

FLASH中,const和代码(.text)存放在图中绿 {MOD}圈圈里

我想知道图中红 {MOD}圈圈的存储格式是什么,因为分散加载到内存中的时候,有一个复制或解压缩过程

我尝试的是在KL02下做的仿真

Region Table的范围是

Region Table为

Region Table里面的格式应该是4个字一组

第一个word表示:源地址

第二个word表示:目的地址

第三个word表示:长度或其他值?

第四个word表示:应该是指定word1和word2位置的数据存储和压缩类型,可能是个结构体

上面没有找到官方的说明,一个老外问过http://www.keil.com/forum/19386/,但也没有人解答

问我为什么这样用,楼主只是想了解一下内部详细的实现方式,以后或许会用的到

希望了解的来告知一下,大家有兴趣的话,也可以谈谈想法

附Keil MDK工程

Blinky.zip

(203.16 KB, 下载次数: 6)

2014-8-26 11:27 上传

点击文件名下载附件

Blinky.zip

(203.16 KB, 下载次数: 6)

2014-8-26 11:27 上传

点击文件名下载附件

Copy of k3.jpg (34.93 KB, 下载次数: 0)

下载附件

2014-8-26 11:18 上传

Copy of k3.jpg (34.93 KB, 下载次数: 0)

下载附件

2014-8-26 11:18 上传

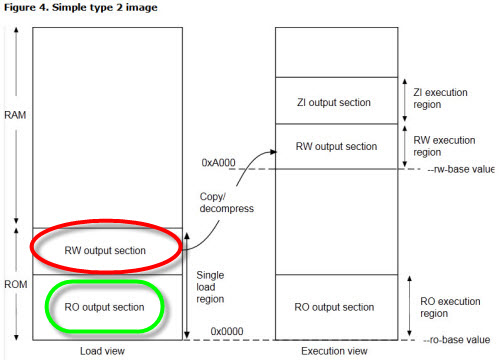

Region Table即位图中红 {MOD}圈圈内的的一部分,另一部分是压缩后的数据,由Region Table指向

FLASH中,const和代码(.text)存放在图中绿 {MOD}圈圈里

我想知道图中红 {MOD}圈圈的存储格式是什么,因为分散加载到内存中的时候,有一个复制或解压缩过程

我尝试的是在KL02下做的仿真

Region Table的范围是

- Region$Table$Base 0x0000070c Number 0 anon$obj.o(Region$Table)

- Region$Table$Limit 0x0000073c Number 0 anon$obj.o(Region$Table)

Region Table为

- 0000 073C

- 1FFF FC00

- 0000 03F4

- 0000 03BA

- 0000 0750

- 2000 0000

- 0000 0014

- 0000 0104

- 0000 0764

- 2000 0014

- 0000 0264

- 0000 0120

Region Table里面的格式应该是4个字一组

第一个word表示:源地址

第二个word表示:目的地址

第三个word表示:长度或其他值?

第四个word表示:应该是指定word1和word2位置的数据存储和压缩类型,可能是个结构体

上面没有找到官方的说明,一个老外问过http://www.keil.com/forum/19386/,但也没有人解答

问我为什么这样用,楼主只是想了解一下内部详细的实现方式,以后或许会用的到

希望了解的来告知一下,大家有兴趣的话,也可以谈谈想法

附Keil MDK工程

Blinky.zip

(203.16 KB, 下载次数: 6)

2014-8-26 11:27 上传

点击文件名下载附件

Blinky.zip

(203.16 KB, 下载次数: 6)

2014-8-26 11:27 上传

点击文件名下载附件

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

ROM和RAM可以放在一个同一个空间,Cortex有三条总线,D、I、S,挂载到I、S的都可以执行指令(貌似是,但我不确定)。。啥啥结构的,书上的东西太老了,甭管

喔。还有待学习。。谢谢。

好好学呢,架构这东西看起来挺有意思的

一周热门 更多>