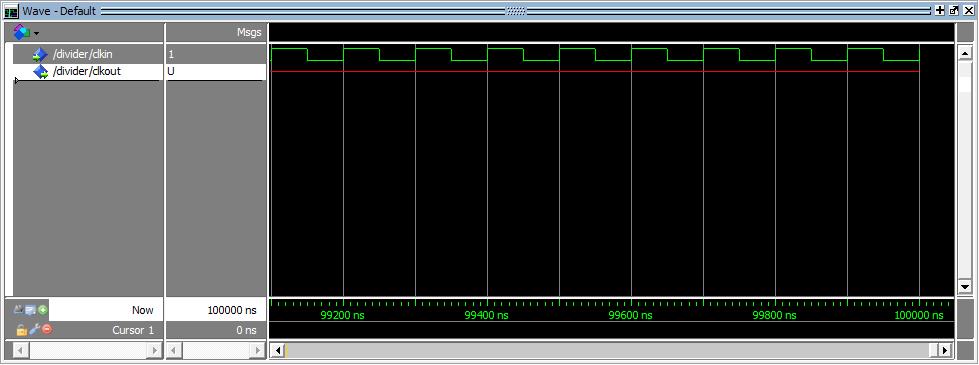

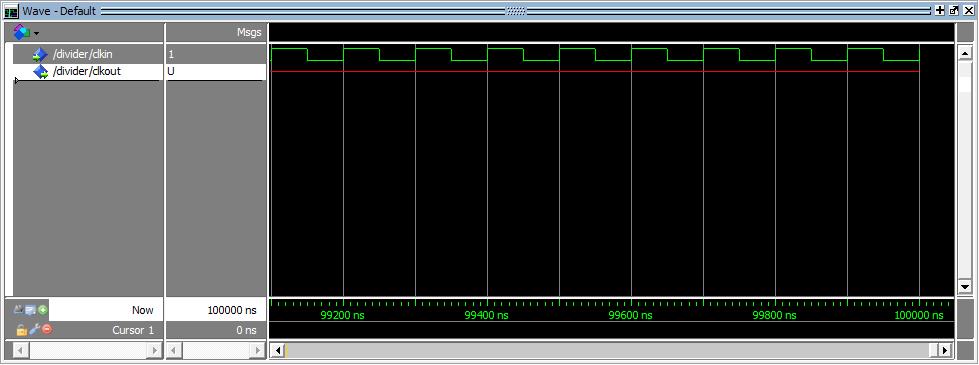

我设计的是九分频的分频器,占空比为50%,在quartus 6.9编译和仿真都能得到结果,但是在modelsim SE 10.1c中却得到这样的

在modelsim SE 10.1c仿真的结果

如果哪位能解释下这种情况和就我的程序给点意见,那就先谢谢了!:)

这是源代码:

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.All;ENTITY divider ISPORT( clkin : IN STD_LOGIC; --输入信号 clkout : OUT STD_LOGIC --输出信号 );END divider ; ARCHITECTURE behv OF divider IS SIGNAL temp: INTEGER RANGE0 TO 8;BEGIN PROCESS(clkin) BEGIN IFclkin'EVENT AND clkin = '1' THEN IFtemp = 8 THEN temp<= 0; ELSE temp<= temp + 1; ENDIF; ENDIF; ENDPROCESS; PROCESS(temp) BEGIN IFtemp < 4 THEN IFclkin = '0' THEN clkout<= '0' ; ENDIF; ELSIFclkin'EVENT AND clkin = '1' THEN clkout<= '1'; ENDIF; ENDPROCESS;ENDARCHITECTURE;

如果哪位能解释下这种情况和就我的程序给点意见,那就先谢谢了!:)

这是源代码:

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.All;ENTITY divider ISPORT( clkin : IN STD_LOGIC; --输入信号 clkout : OUT STD_LOGIC --输出信号 );END divider ; ARCHITECTURE behv OF divider IS SIGNAL temp: INTEGER RANGE0 TO 8;BEGIN PROCESS(clkin) BEGIN IFclkin'EVENT AND clkin = '1' THEN IFtemp = 8 THEN temp<= 0; ELSE temp<= temp + 1; ENDIF; ENDIF; ENDPROCESS; PROCESS(temp) BEGIN IFtemp < 4 THEN IFclkin = '0' THEN clkout<= '0' ; ENDIF; ELSIFclkin'EVENT AND clkin = '1' THEN clkout<= '1'; ENDIF; ENDPROCESS;ENDARCHITECTURE;

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

试试~

你给个初始值试试。

一周热门 更多>