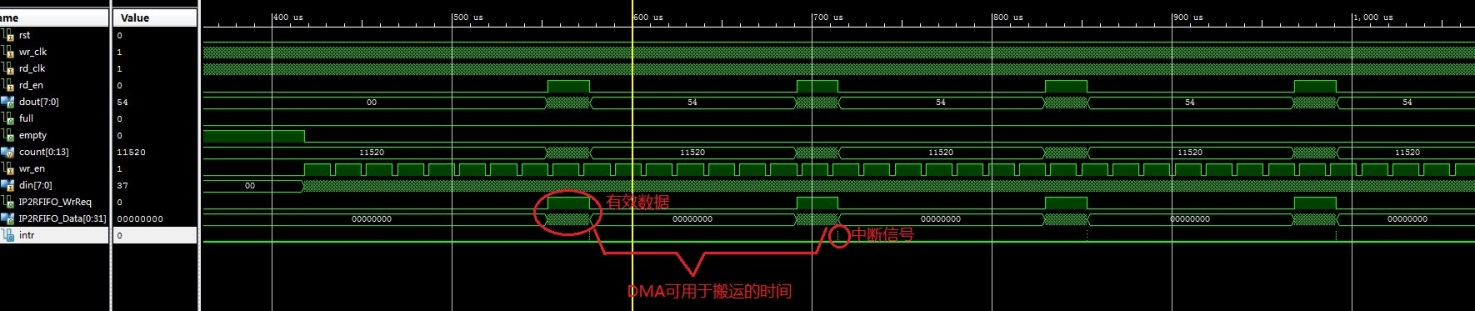

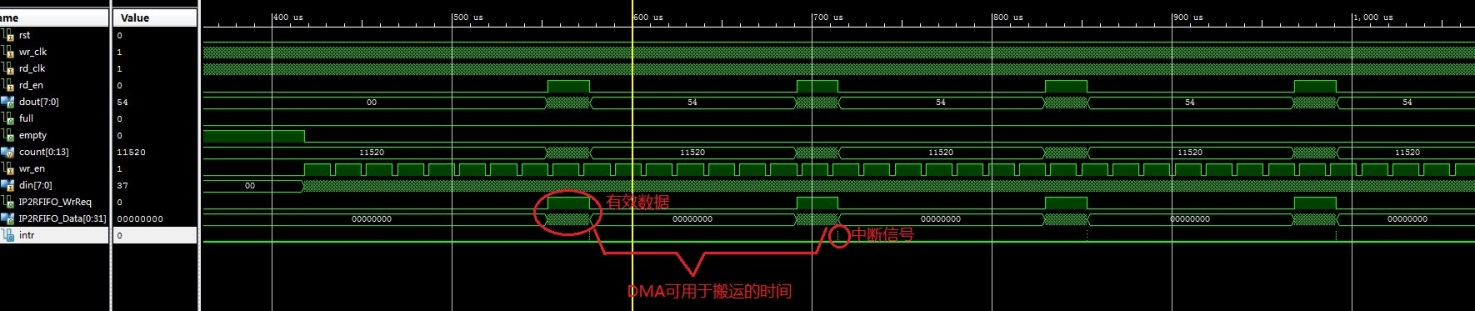

最近被dma弄得头疼,使用dma将fifo中的数据搬运到ddr中,搬运是可以进行的,但是速度却似乎达不到实时要求。 数据源是一个pal的视频流信号,经过fifo处理后,将27MHZ的有效数据流转换为了PLB_CLK(125MHZ)的数据流,可以得出,这时候信号线上,无效数据时间:有效数据时间 >4;每行的有效数据写入fifo后,立刻产生一个中断intr,然后利用dma将这些数据搬到ddr中。

结果却不尽人意,在sdk中看到,数据只是最开始的一段是正确的,检查了很久都没发现错误原因,后来读取dma状

态寄存器(进入中断就马上读取),发现除开第一次之外,dma都处于正在搬运的状态,也就是说,中断之后,dma开

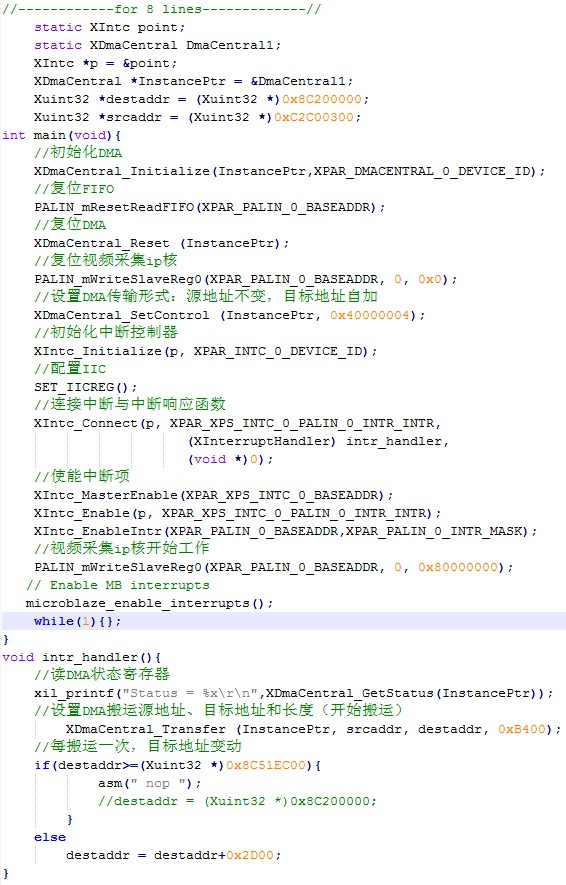

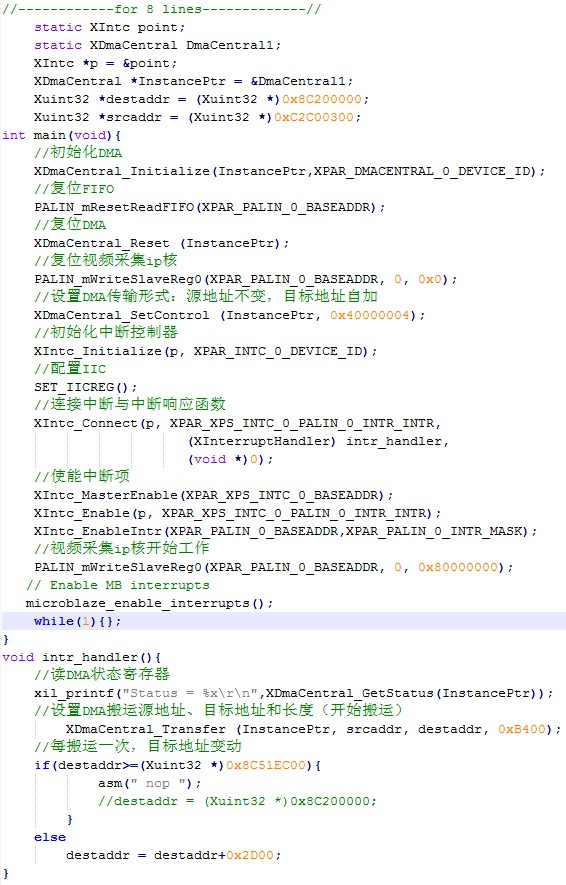

始了搬运,但是在下一次中断来临之前,搬运并没有结束。这样必然导致后面的数据出错。下面是控制程序:

DMA作为大家公认的高速传输设备,速度应该是不会这般慢的,应该是我的设计存在问题,但小弟实在是检查不出问题

所在,所以发帖请教论坛的诸位大神。希望大神能为我指出问题所在,万分感激!

结果却不尽人意,在sdk中看到,数据只是最开始的一段是正确的,检查了很久都没发现错误原因,后来读取dma状

态寄存器(进入中断就马上读取),发现除开第一次之外,dma都处于正在搬运的状态,也就是说,中断之后,dma开

始了搬运,但是在下一次中断来临之前,搬运并没有结束。这样必然导致后面的数据出错。下面是控制程序:

DMA作为大家公认的高速传输设备,速度应该是不会这般慢的,应该是我的设计存在问题,但小弟实在是检查不出问题

所在,所以发帖请教论坛的诸位大神。希望大神能为我指出问题所在,万分感激!

一周热门 更多>